Hello,

We designed some custom FGPA firmware with our own Ethernet stack we tested the firmware with development boards and now we've designed a custom PCB where we are trying to implement the system. The main problem we have now is that the RGMII is not working properly. I wanted to access the chip via MDIO to try to solve it, but it's not working neither.

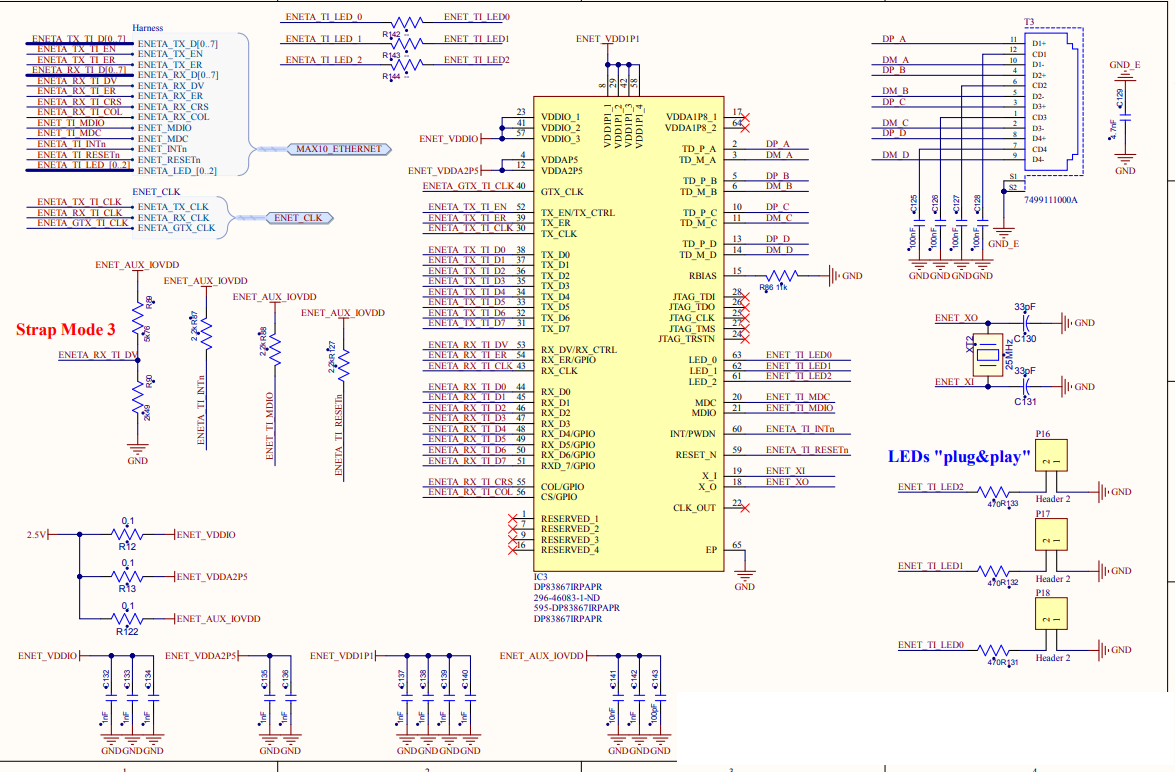

I have output signals, so the chip is doing something, anyway, I'll first want to fix the MDIO problem. This is the schematic:

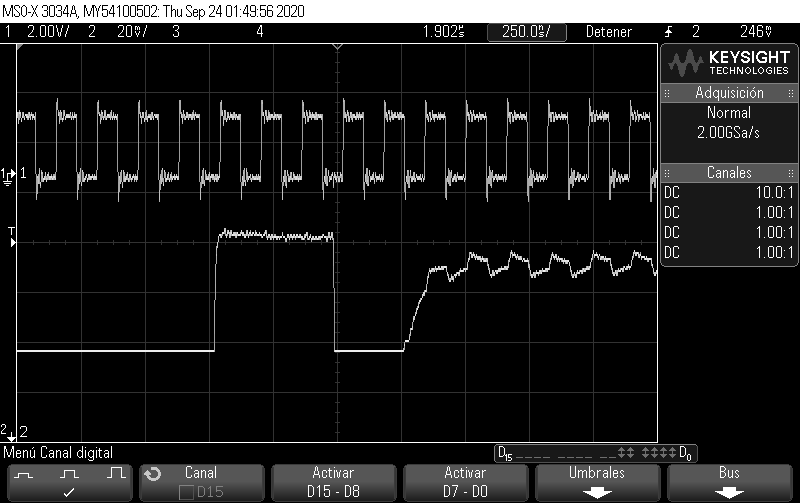

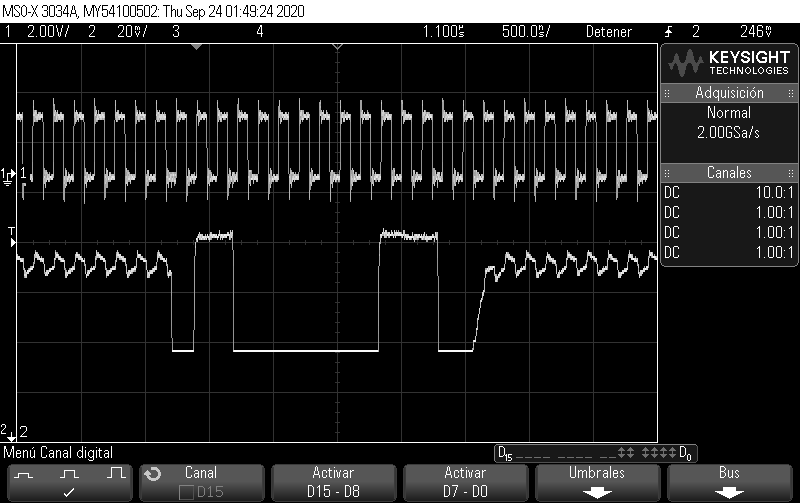

And that's what I'm seeing when looking at the MDIO:

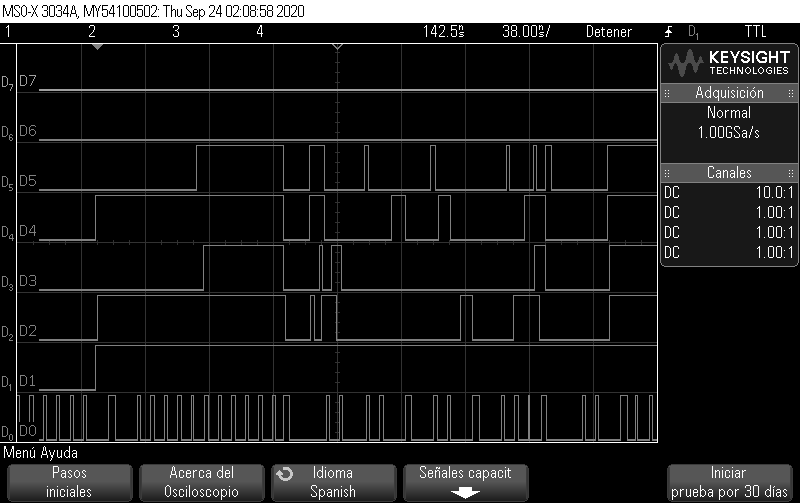

I'll also add some images of the TX RGMII not working properly.

D0: Tx CLK, D1: Enable, From there Data from 0 to 3.

Any ideas? To communicate we are using an FPGA, it has worked with other chips.

Thanks,

GG