Hi Ti Team,

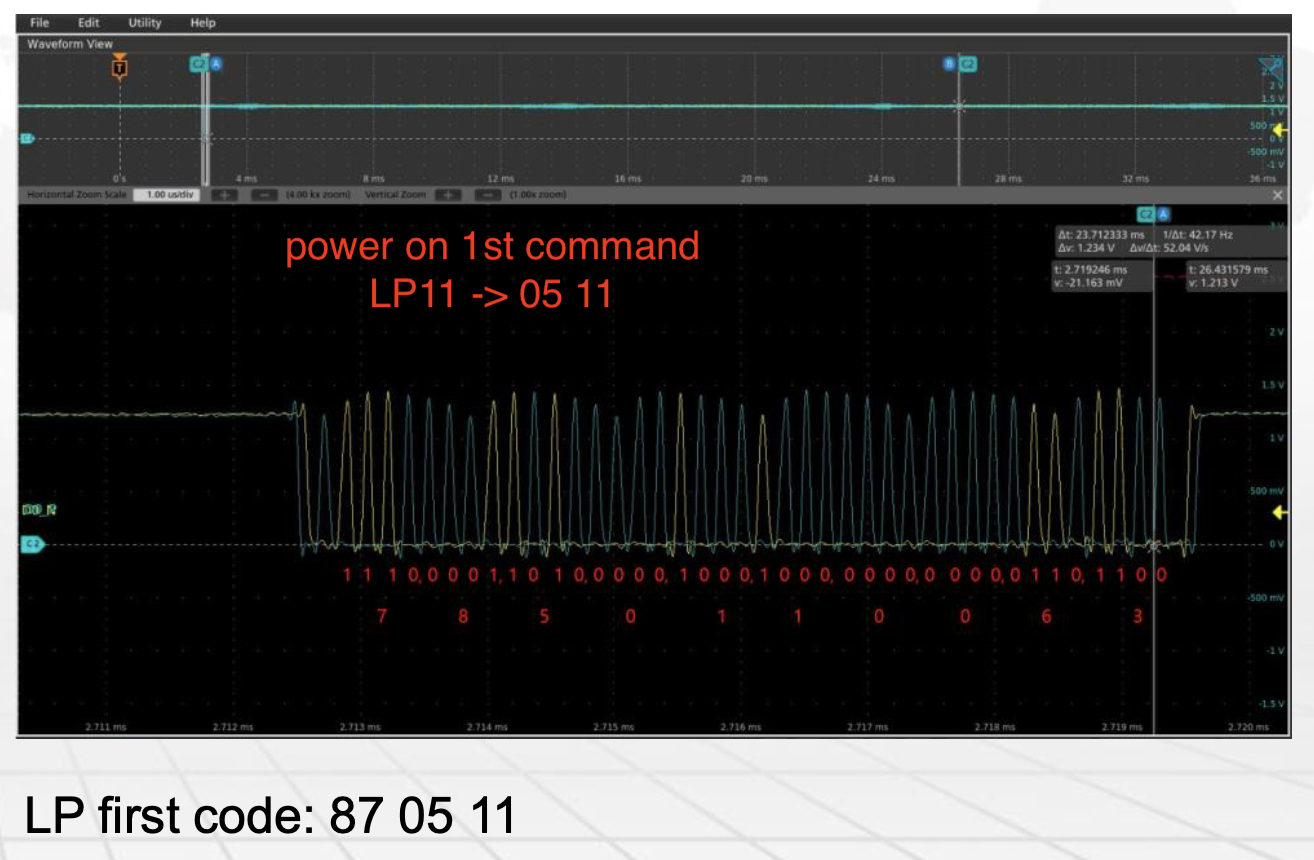

I got an abnormal behavior using SN65DPHY440SS since last year. My display DIC failed to get sleep out command at 2nd time display on (i.e. display on, display off, then display on again). It is proved that Sleep out (05 11) was not sent at the output of SN65DPHY440SS. Could you help with some advice regarding the re-timer and its ULPS mode?

Setup: FPGA MIPI host -> re-timer -> Display DIC

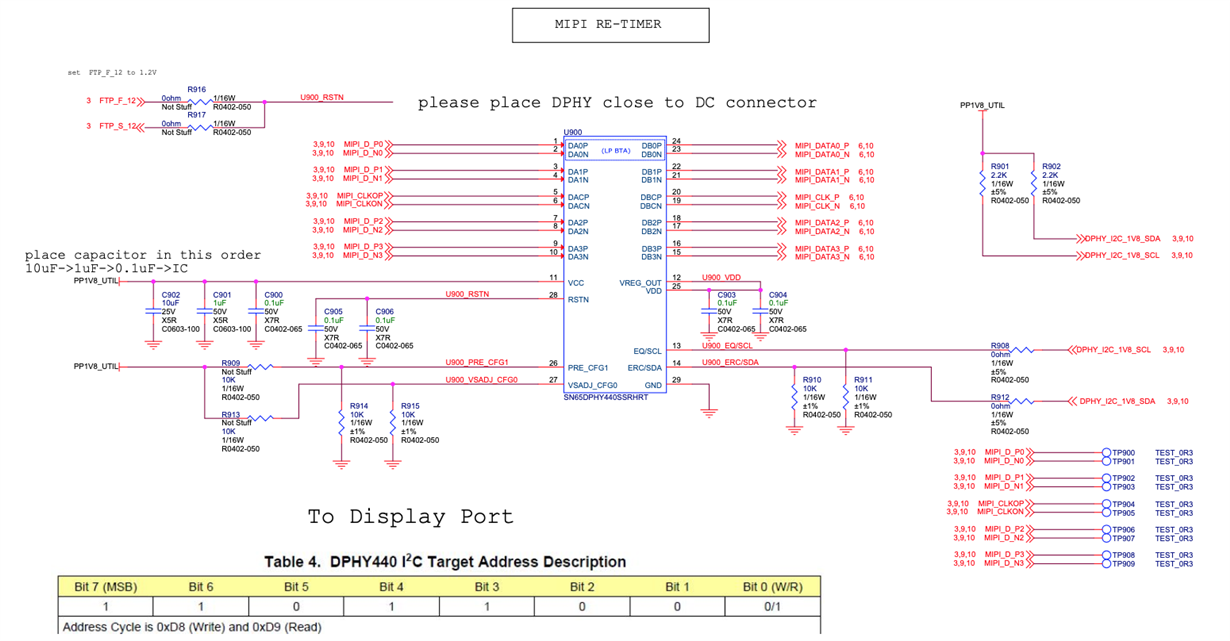

HW Schematic: SN65DPHY440SS has reset constantly pulled up to power supply. I am expecting it is always active.

MIPI command: we have probed the input of re-timer, both display on & off does not send 00011110 command (trigger ULPS mode)

2nd display on shows not Sleep Out waveform at the output of SN65DPHY440SS.

Hypothesis: SN65DPHY440SS entered the ULPS mode.

Workaround: add delay 40ms to activate the re-timer, then send 05 11. It was proved 100% display on every time.

I could not find more info regarding ULPS on the data sheet.

Thanks,

Nu