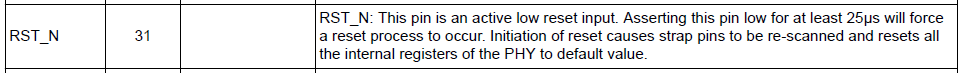

Other Parts Discussed in Thread: DP83822I

Hello Texas Instruments team,

We recently purchased two DP83TD510E-EVM boards for evaluation in hope to migrate our Ethernet products over SPE.

We would like to connect 2 x EVM boards via SPE and communicate with a laptop at each end of the RJ45 connectors and run a Jperf speed/network test

Have run through the Board Setup process in the User Guide.

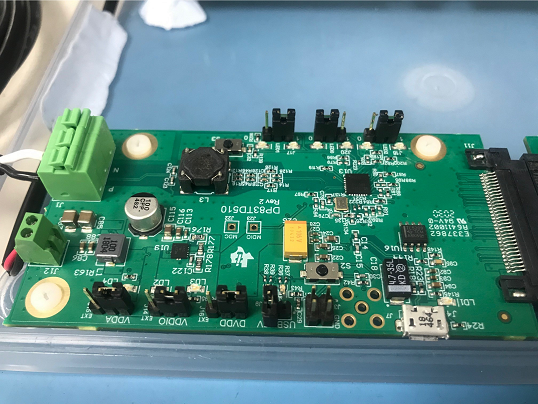

- External 12V DC Supply connected to J12, total I ~ 0.08A for 2 boards.

- Measured all onboard supply rails are fine.

- We have set both our boards, following User Guide Section 3.2.1 to RMII Master Mode for DP83TD510 providing 50Mhz Clock to DP83822 (Slave) via R149 (PCB Factory Default)

- LED_0 is strapped low at J20 on both of the EVM boards.

- SPE link cable 1m twisted pair

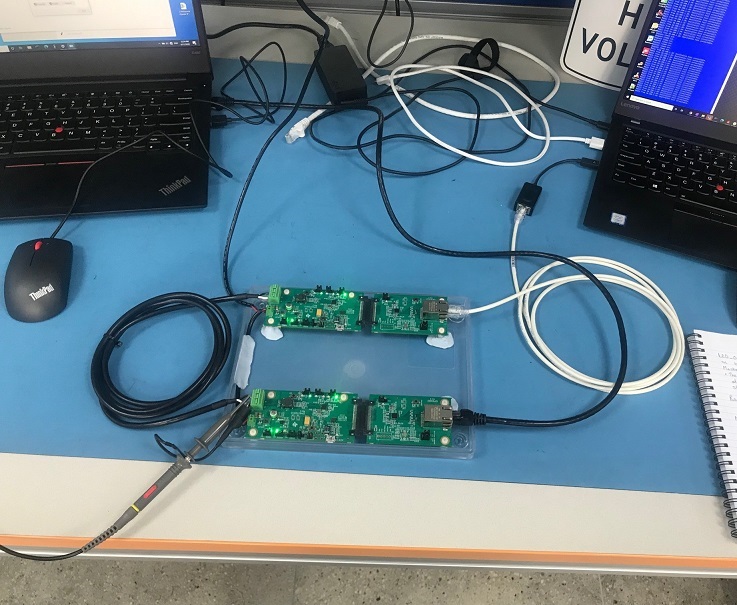

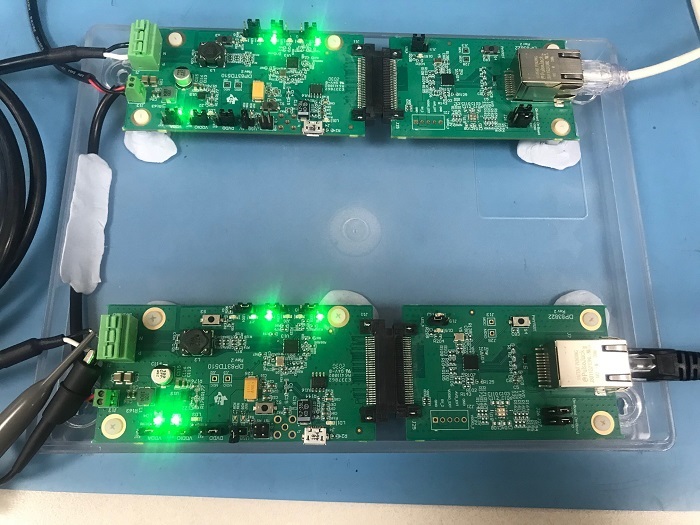

The following is our image details our setup:

We have also downloaded the USB2MDIO Tool to downloaded one scripts at a time that we discovered via the forum post, with no success in linking between boards A & B.

Combinations we tried below:

|

DP83TD510E-EVM - Board [A] |

DP83TD510E-EVM - Board [B] |

|

AutoNegotiation_Initialization.txt |

AutoNegotiation_Initialization.txt |

|

Force_1Vpp_Master_Init.txt |

Force_1Vpp_Slave_Init.txt |

|

Force_2v4Vpp_Master_Init.txt |

Force_2v4Vpp_Slave_Init.txt |

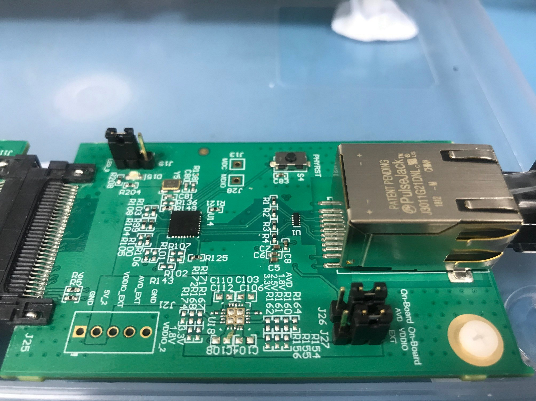

Both RJ45 Jack Green LED illuminates & LED (D15) turns OFF, when link to laptops are successful, providing an Ethernet link @ 10Mbps.

On the SPE board we see LED_1 illuminate on power up, LED_0 only turns on occasionally for what seems to be a few seconds before it drops off again. (See Image below)

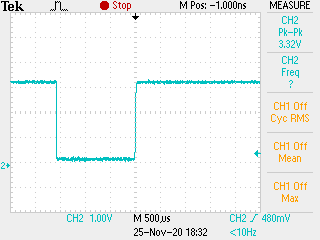

Below is a zoomed out CRO snapshot of the SPE pk-pk when there is a link LED_1 present for a few seconds before it drops off, and the pk-pk of this signal goes down to 1V, and then it continues to attempt again.

Note: Disregard the gap in the signal, due to shifting the screen cap horizontally.

Another zoomed in screen cap below, when there was no link LED_1 present:

What could we be missing here to achieve SPE Link between the devices?

Question, do we need to set 1 x EVM to RMII Master & the other EVM to RMII Slave in order to pair the two together?

Which means populating,/removing resistor straps detailed in section 3.2.2 for EVM Board (B)?

Thanks in advance,

Daniel Haddad

Engineering Manager

Pixel Technologies