Part Number: DS110DF111

Other Parts Discussed in Thread: USB2ANY

Hello,

Our customer used EEPROM mode to configure DS110DF111SQ, it couldn't link of SFI interface. But when configured with PIN control mode, it could link normally.

1.PIN control mode, normally link.

De-Emphasis Setting:DEMA/B=0(0db)

2. EEPROM mode, SFI interface couldn't link. The registers are as following:

REG 00x2F[7:4]=1100;//10.3125 Gbps data rate。

REG 0x31[6:5]=00; //Adapt mode 0。

REG 0x2D[3]=1;//override the EQ setting。

REG 0x03[7:0]=00; //EQ=0。

REG 0X3A[7:0]=00;

REG 0x40[7:0]=00;

REG 0x1E[3]=1;//Disable the DFE。

REG 0x2d[2:0]=000;//Driver VOD 600mv。

REG 0x15[2:0]=000;//De-Emphasis 0db。

REG 0x09[5]=1;//Enable Override Output Mux。

REG 0x1E[7:5]=000; //Select RAW data (CDR Bypass)。

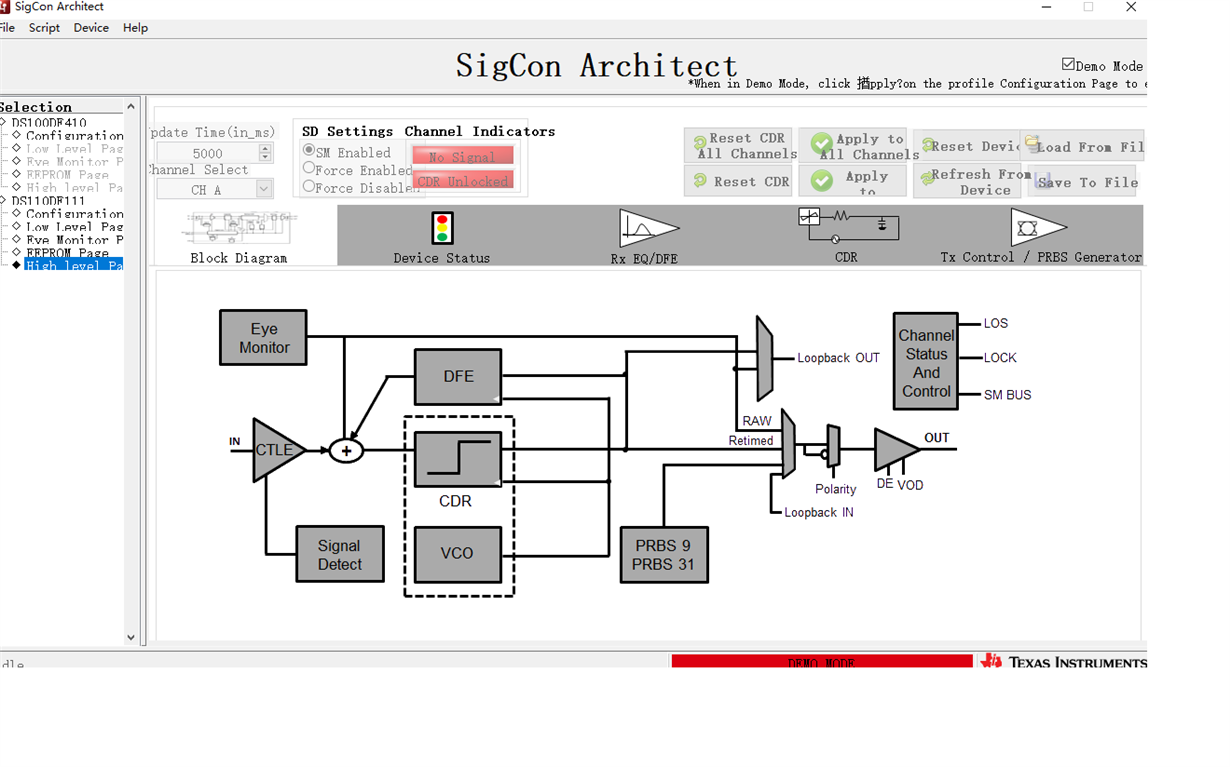

In addition, when using EEPROM mode, do we need DPS-DONGLE-EVM or USB2ANY tool? Or DPS-DONGLE-EVM or USB2ANY need only in SMbus slave mode? But without DPS-DONGLE-EVM or USB2ANY tool, the high level page couldn't detect the status of SigCon Architect .Please refer to the below screen of high level page.

Our customer used SigCon Architect to generate the HEX file and downloaded it into EEPROM, and then he tested LOS and lock pin are always low level. Could you please help to analyze?

Best regards

kailyn