Hi Team,

DP83822 is transformerless configuration and connected to LAN9500, both of DP83822 and LAN9500 are configured to fixed 100Mbps and auto-crossover.

However, it's found that DP83822 shows to be link up and link down continuously, while LAN9500 is always link up.

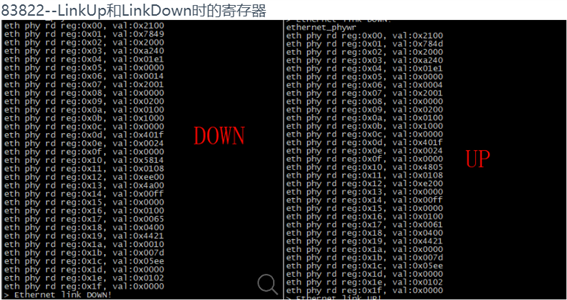

When linked up, the 0x01 registers value is 0x4805 which tells that the signal detect is 0 and false carrier sense latch is 1, then it will become to link down. The registers value when the link is up and down is as below:

My questions are:

1. What does the false carrier sense mean here? What are the possible reasons for this fault?

2. The parallel detection fault also happens, what's the possible reason?

3. Is there any recommendation for this kind of continuous link up and down such as register configuration?

Thanks and Best Regards!

Hao