Part Number: SN65DSI85

hi Sir.,

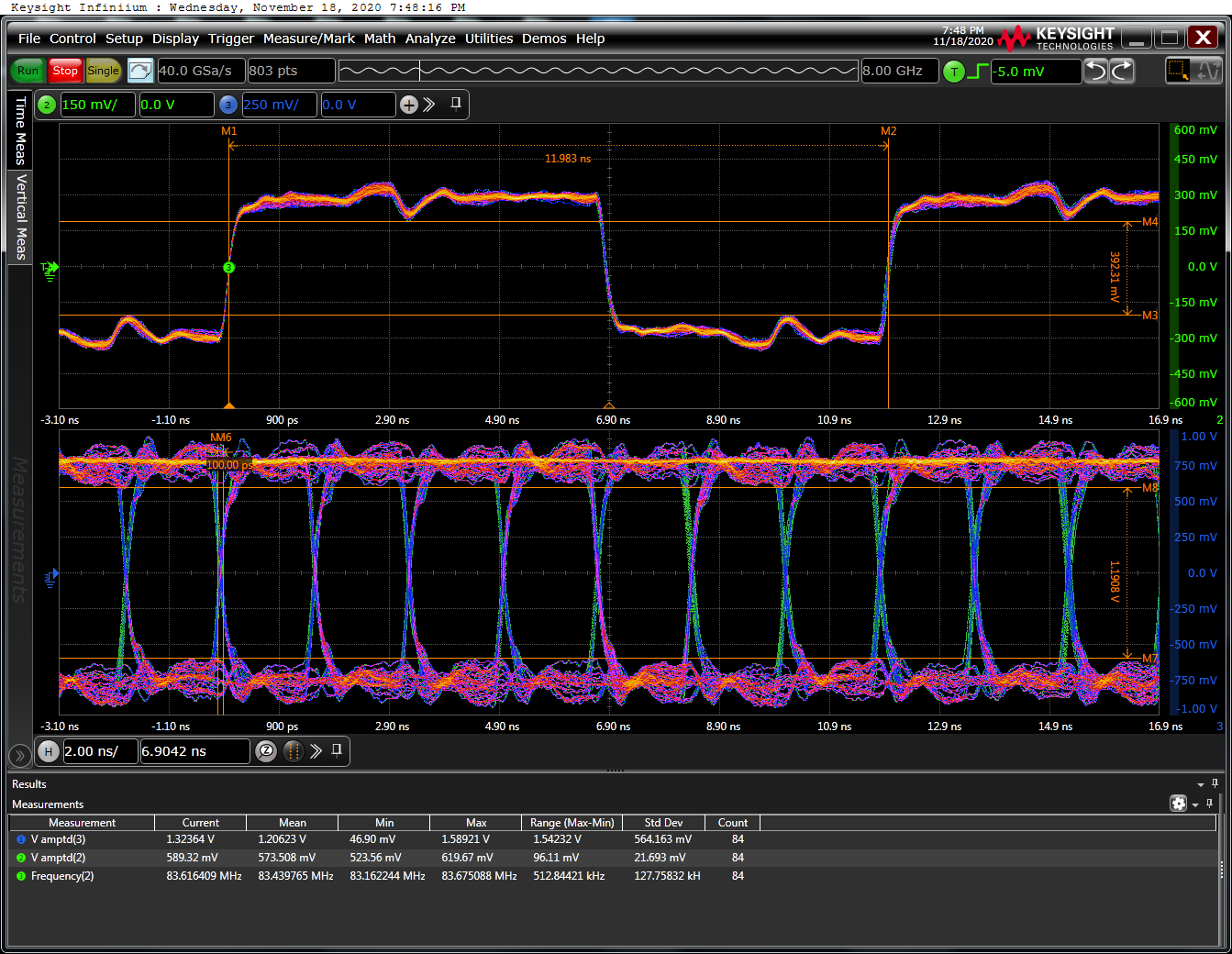

my customer measure the LVDS clock and data output from SN65DSI85. the clock amplitude looks correct but data looks 2x comparing with spec.

the register 0x19 is 0x0F. register 0x1A is 0x00.

the data amplitude seems 2x higher than spec. They try other different value on register 0x19, it all looks the same.

|

Configure |

0x19.6 |

0x19.4 |

0x19.2\3 |

0x19.0\1 |

CLK(mv) |

Data(mv) |

|

|

Default |

0 |

0 |

00 |

00 |

194 |

468 |

|

|

1 |

0 |

0 |

01 |

01 |

260 |

800 |

|

|

2 |

0 |

0 |

10 |

10 |

330 |

950 |

|

|

3 |

1 |

1 |

00 |

00 |

180 |

520 |

|

|

4 |

1 |

1 |

11 |

11 |

380 |

1050 |

|

|

5 |

0 |

0 |

11 |

11 |

390 |

1190 |

|

any idea?

How to separately control the the data and clock amplitude

BR,

frank