Other Parts Discussed in Thread: DS250DF230, DS250DF210,

I have the board setup to try to get the loop back mode working, but I am not able to get CDR lock. I am supplying 3.3V to the board.

- On the p5 of the EVM User's Guide, it shows that I need to install J41 and leave J45 open. I just want to confirm that's a misprint. I have J41 open and installed jumpers to J45 so there's 2.5V to the chip.

- I have to MXP40 connectors connected to the board, and have the signals go from TX0P --> RX0P, TX0N --> RX0N, etc... for all the signals.

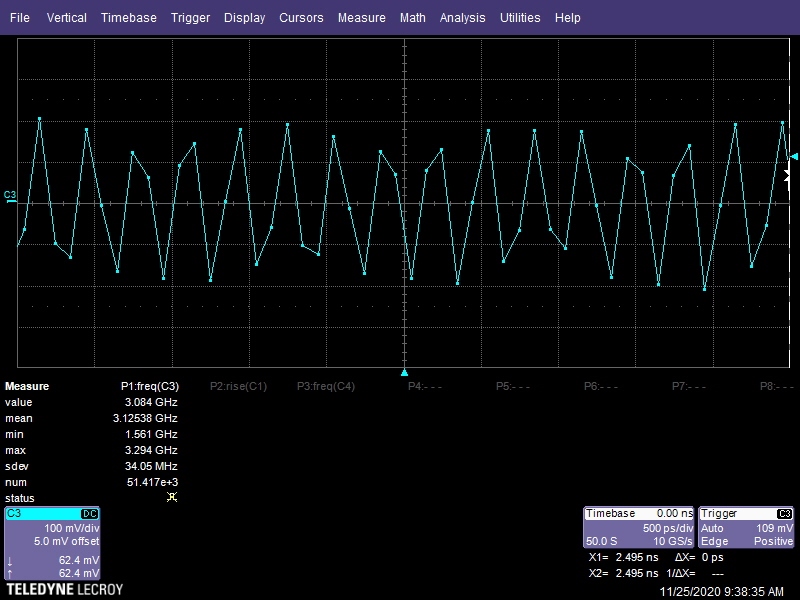

- The best that I could ever get was "Signal Detected" on Channel 1 (but not on Channel 0), and I am not able to get CDR Lock.

- Can you let me know what I need to do to get CDR Lock?

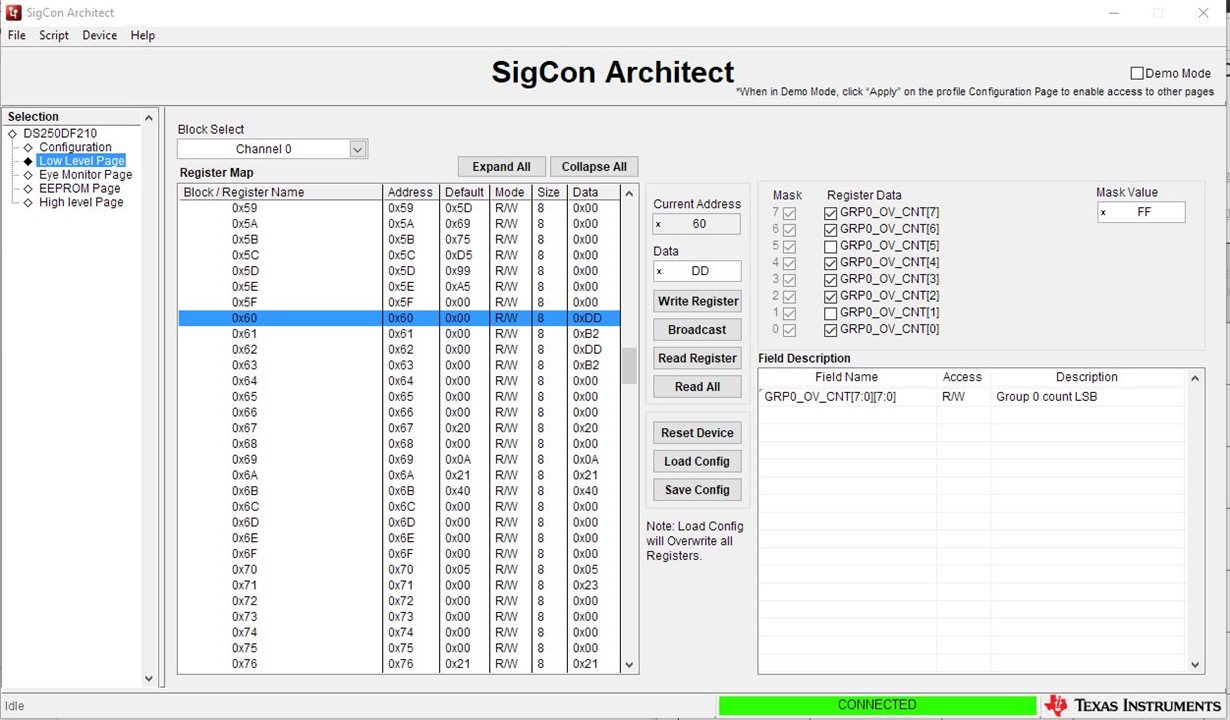

On the CDR Tab I have: Pre-LOCK Output: Pattern Generator, Post-Lock Output: Retimed Data, Data Rate: 10.3125 Gbps

PRBS Gen/Checker: Enable, PRBS31.

Thank you very much for your help!

Jack Lin