Other Parts Discussed in Thread: DS90UB954-Q1, ALP

We use the FPD III link. Here a question arose, where you can certainly support us:

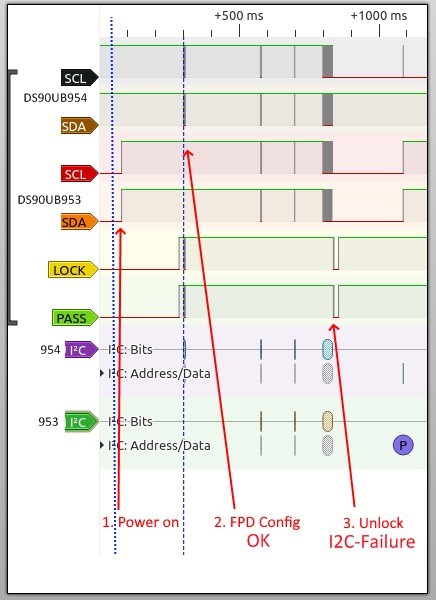

During I2C communication to connected I2C slaves (serializer) in the initialization phase of the link, the link sometimes loses its PASS/LOCK for a short time and the I2C transfer stalls/fails: The FPD link ( also MIPI image data transfer) works well once the initialization has been successful.

The unlock of the FPD-Link occurs the more often, the earlier after the FPD-Link initialisation the I2C communication is started. The unlock is independent of which component is communicating via I2C.

The problem no longer occurs if communication is started several seconds after PowerON of the link (e.g. continuous reading from an EEPROM several seconds after system start).

Our assumption: The FPD-Link connection is unstable during AEQ at power-on if data is already being transferred during this time.

Is our assumption about the cause of the error correct?

What could we adapt (e.g. AEQ register settings, link training, etc.) to make the link "stable" more quickly after power-up?

What further investigations would be appropriate to find out more about the "error"?

Translated with www.DeepL.com/Translator (free version)