Other Parts Discussed in Thread: DSI-TUNER

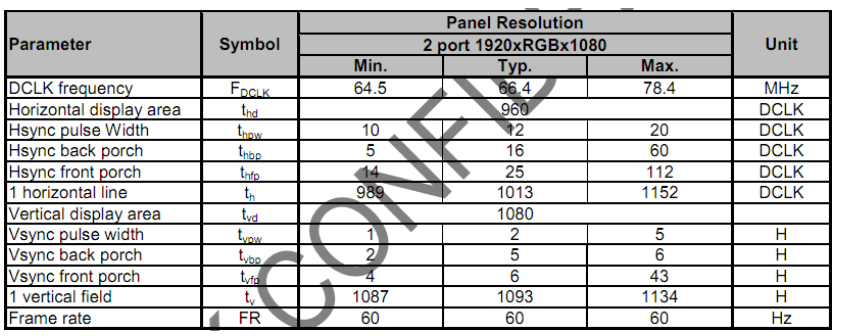

Our dsi config works fine with a dsi-interface panel, and the dsi dphy bitrate is 900Mbps.

data path is:dsi source (900Mbps) --> sn65dsi94 --> lvds panel

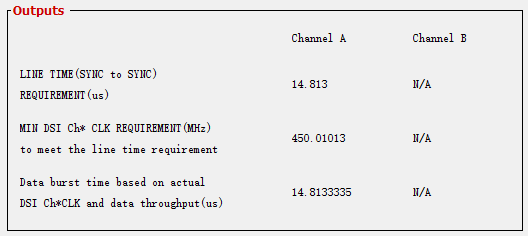

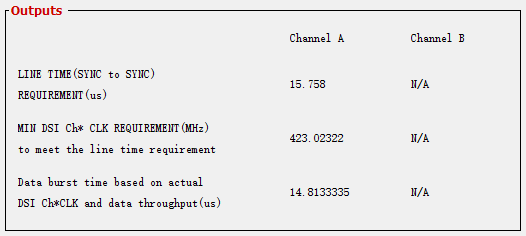

I just can't get the the 2 times in Ouputs window the same.

How can i get the dsi source correctly convert to lvds the panel needed?

Do i have to change the dsi dphy bitrate so that the lvds clk can perfectly match?

Here is my dsi status configuration, plz help.

Thanks a lot.https://e2e.ti.com/cfs-file/__key/communityserver-discussions-components-files/138/pj5801g02.7z