Hello Team,

The DP83826 highlights integrated MAC and MDI terminations on the first page.

The Electrical Characteristics section list the pins that have the MAC series termination resistors.

So I know which pins have the integrated MAC terminations.

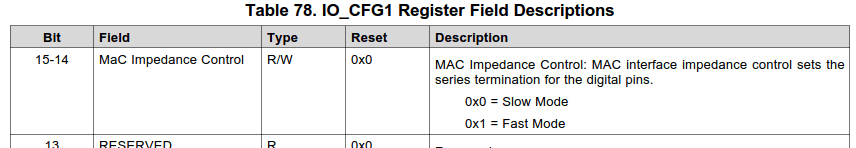

Table 78 for register IO_CFG1 shows a Slow Mode and a Fast Mode setting for MAC Impedance Control.

Are these modes related to the 50-Ohm MAC series termination resistor value specified in the Electrical Characteristics section?

What does Slow and Fast mean?

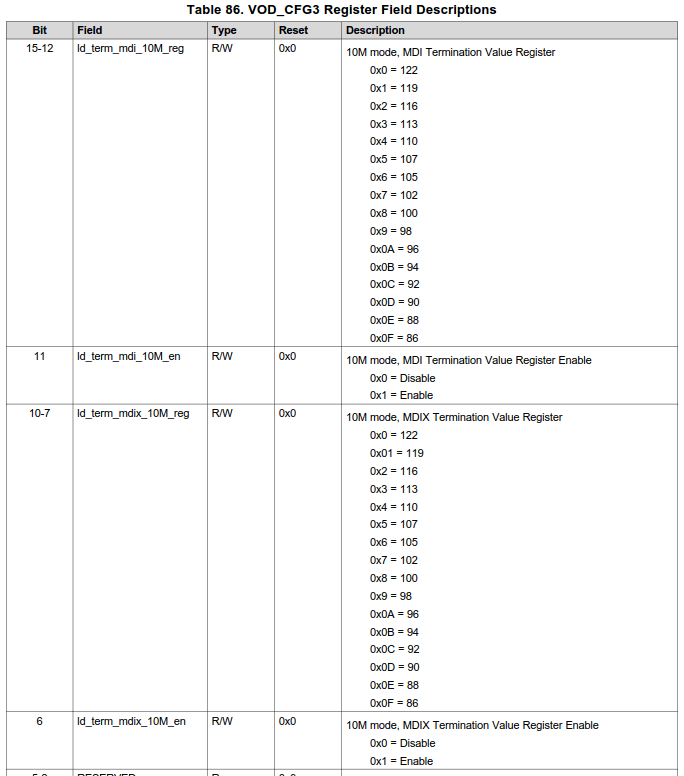

Table 78 for register VOD_CFG3 has settings for MDI and MDIX termination values.

Are these settings only for 10 Mbps and not available for 100 Mbps?

Why are there two sets of termination values, one for MDI (straight-through?) and one for MDIX (cross-over?)?

Thanks,

SunSet