Other Parts Discussed in Thread: DS90UB962-Q1, DS90UB960-Q1

Hello,

Below is a summary of the clarification provided by the FPD-link team for some questions related to 953-964.

@FPD-link team, Please confirm.

Q1: Can 953-964 support YUV422-8 bit? In other words, the input to 953 is YUV422-8 bit, can this be transmitted to the 964? I assume this can be done using "Non-sychronous external clock" mode (Table 7-6) in the 953 datasheet.

A1:The challenge here is that 964 only supports DVP mode. So, "Non-synchronous external clock mode" is not supported between 953/964.

Natively YUV422 8 bit is not supported in DVP mode since the pixel packing structure does not match the CSI-2 standard.

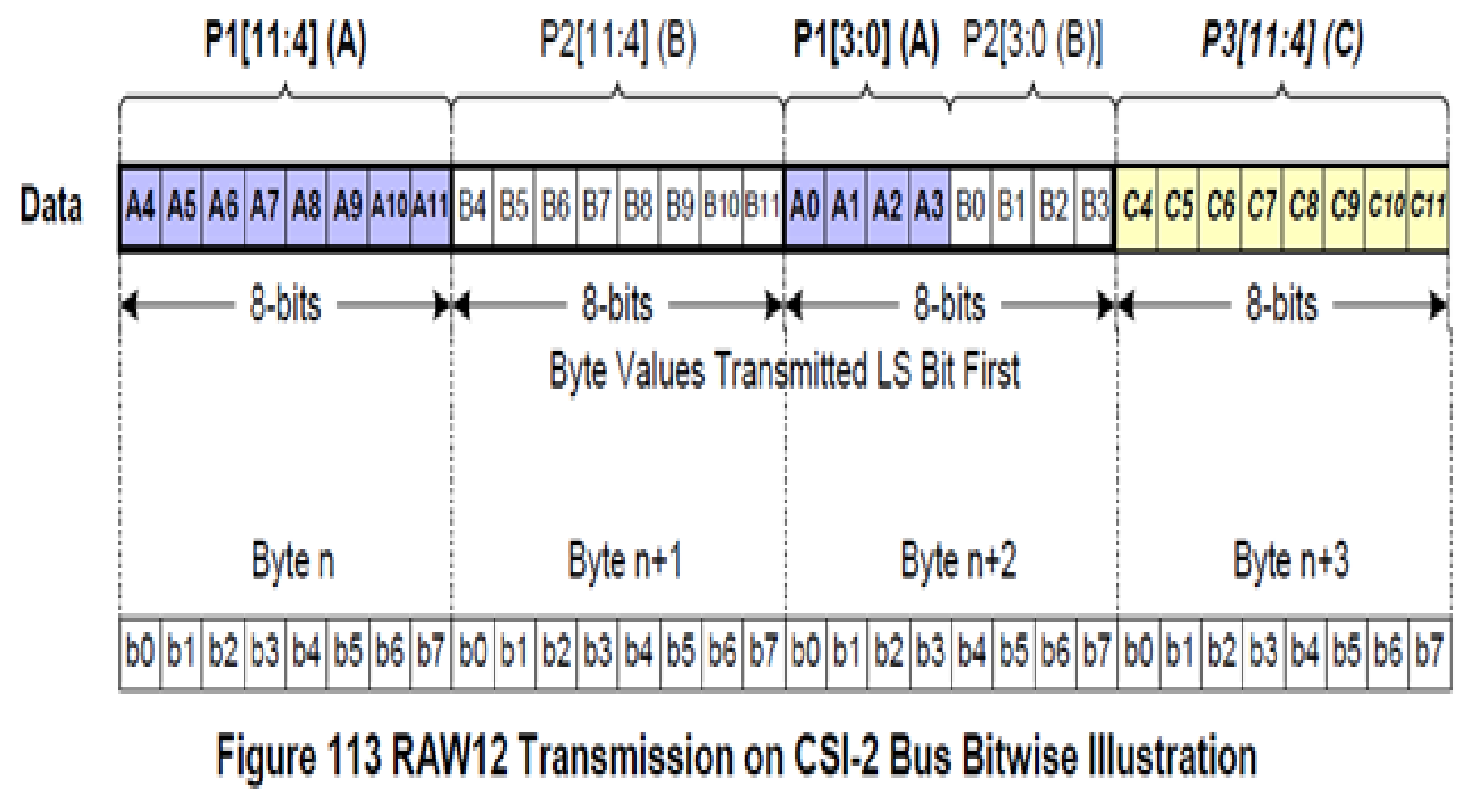

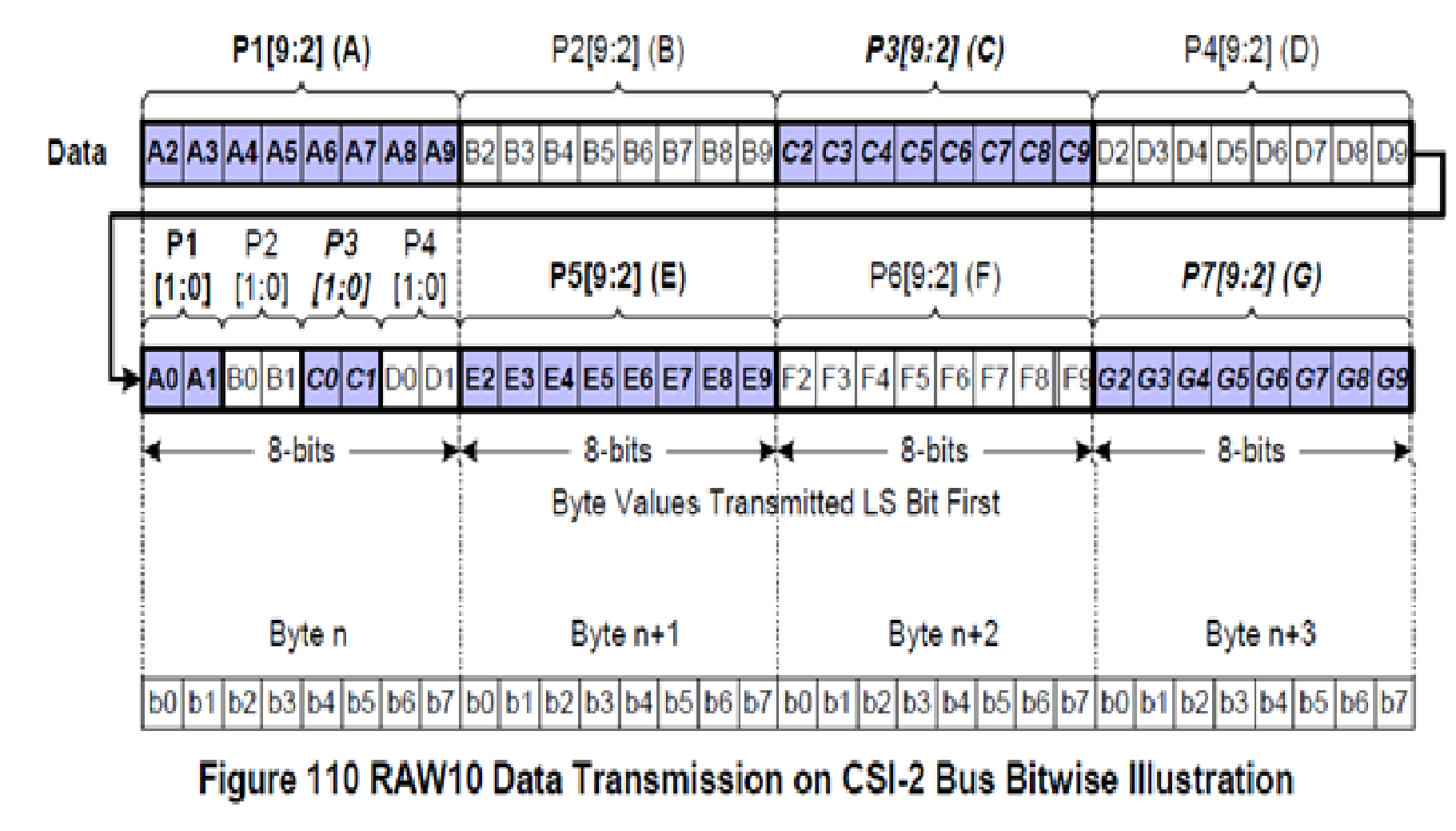

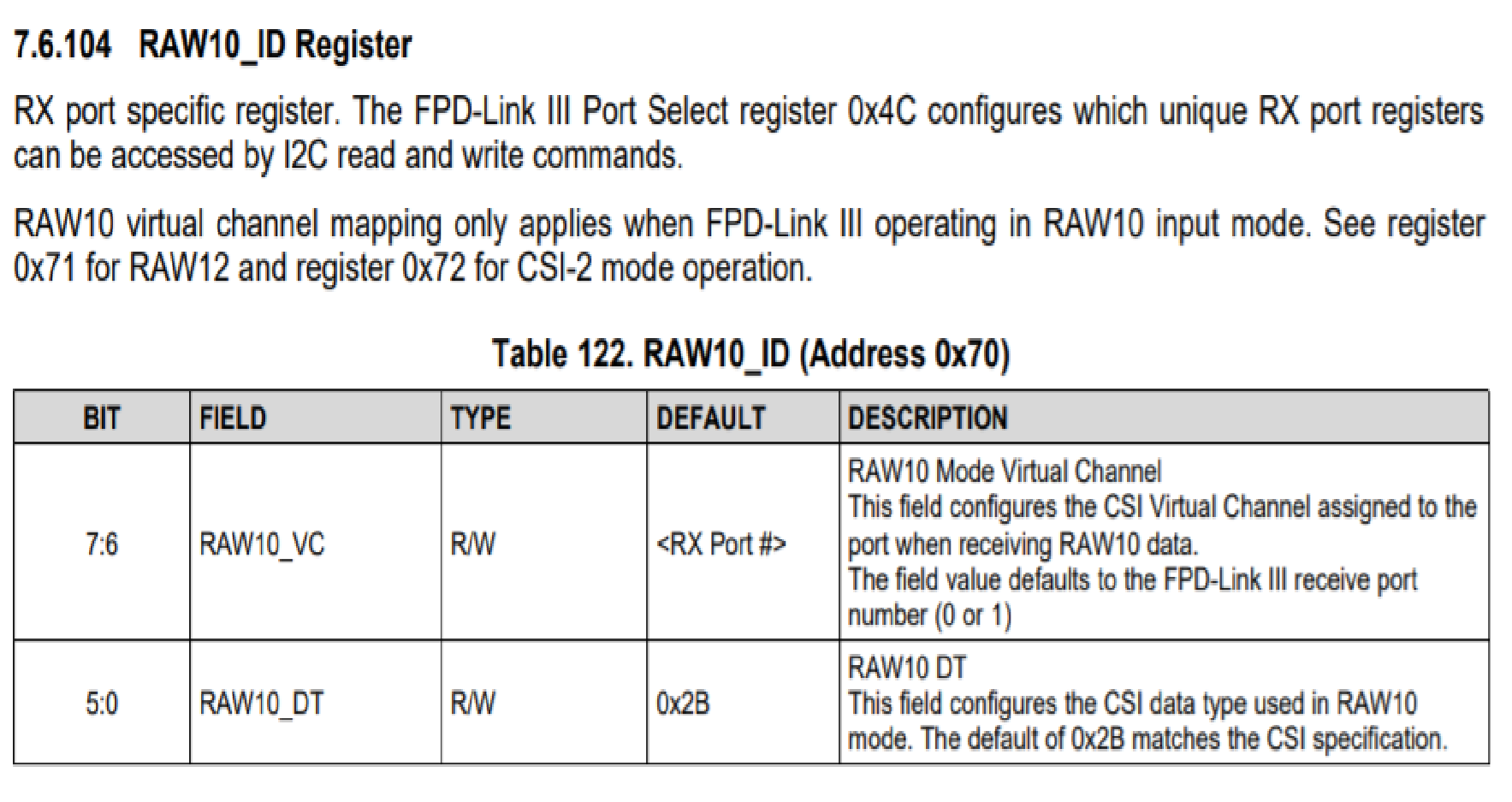

However, there is one alterative. You can technically send YUV422 8-bit data in a custom data structure which uses RAW10 or RAW12 pixel packing, and then on the deserializer side, the SoC would need to know to expect this custom pixel packing structure and extract the data accordingly.

Best regards,

Ahmed