Hi,Ti

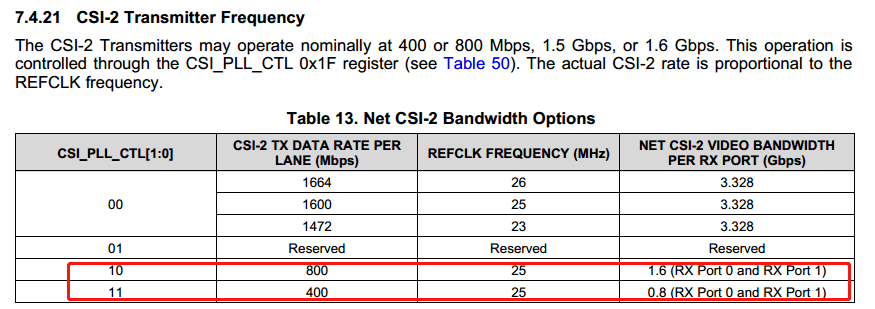

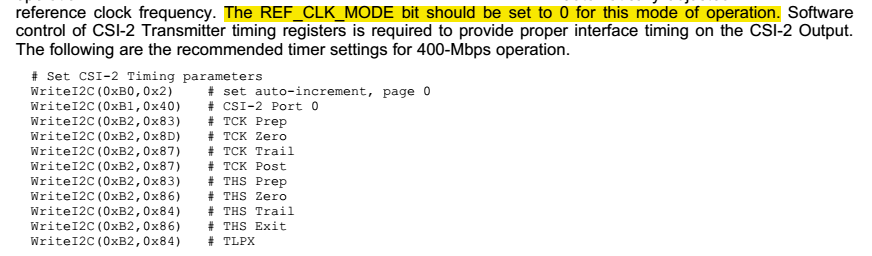

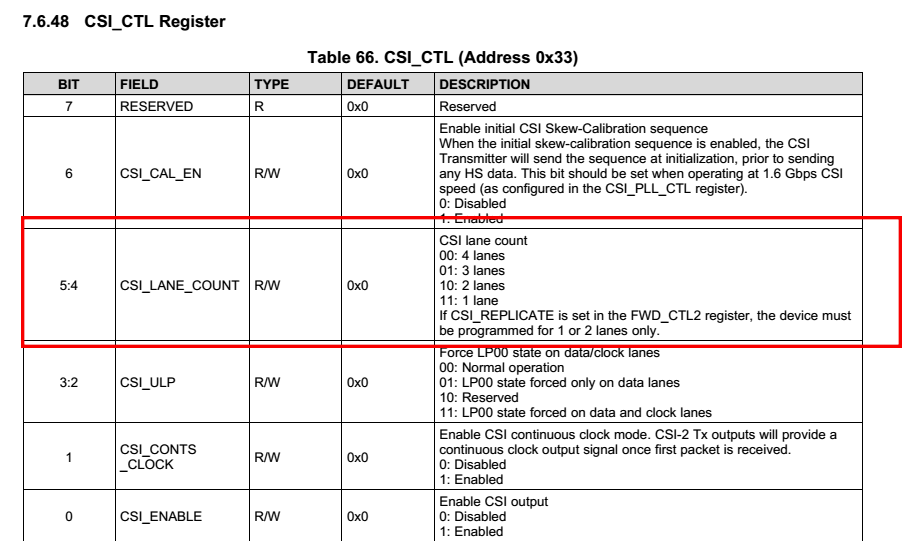

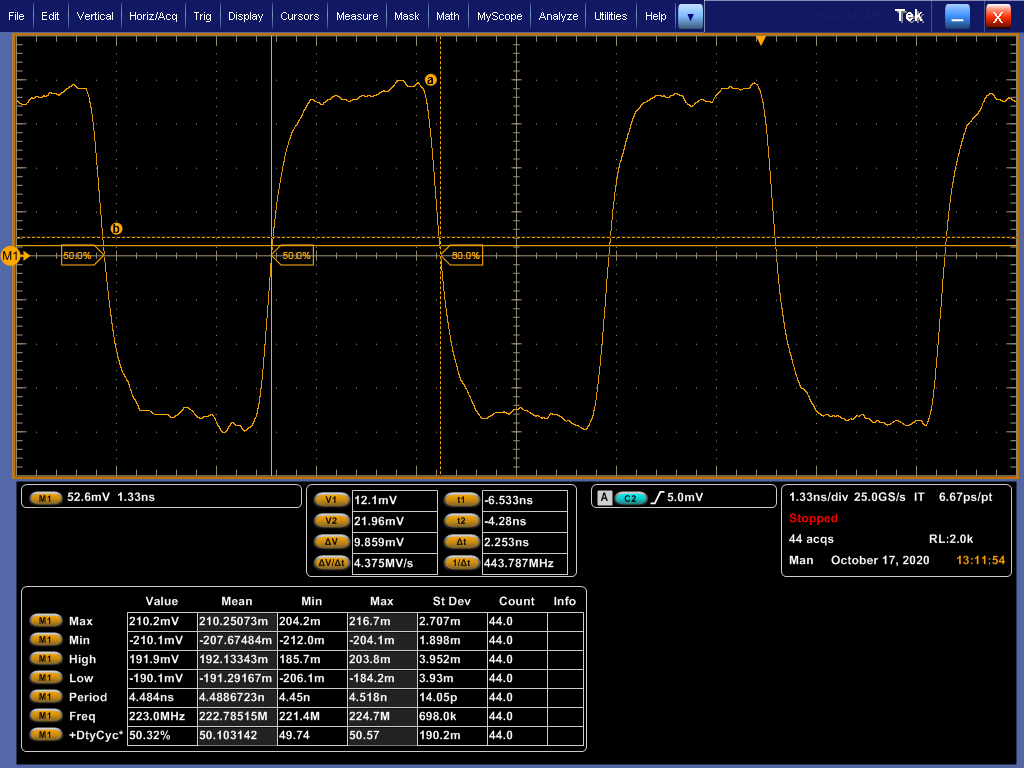

When I set the sensor data input of DS90UB953 to 400bps,The output of the DS90UB954 set to 400bps cannot display the image,I set DS90UB954 to the output of 800bps to display the image normally.

What is the reason and what parts need to be set up?