Part Number: SN65DP159

Hi:

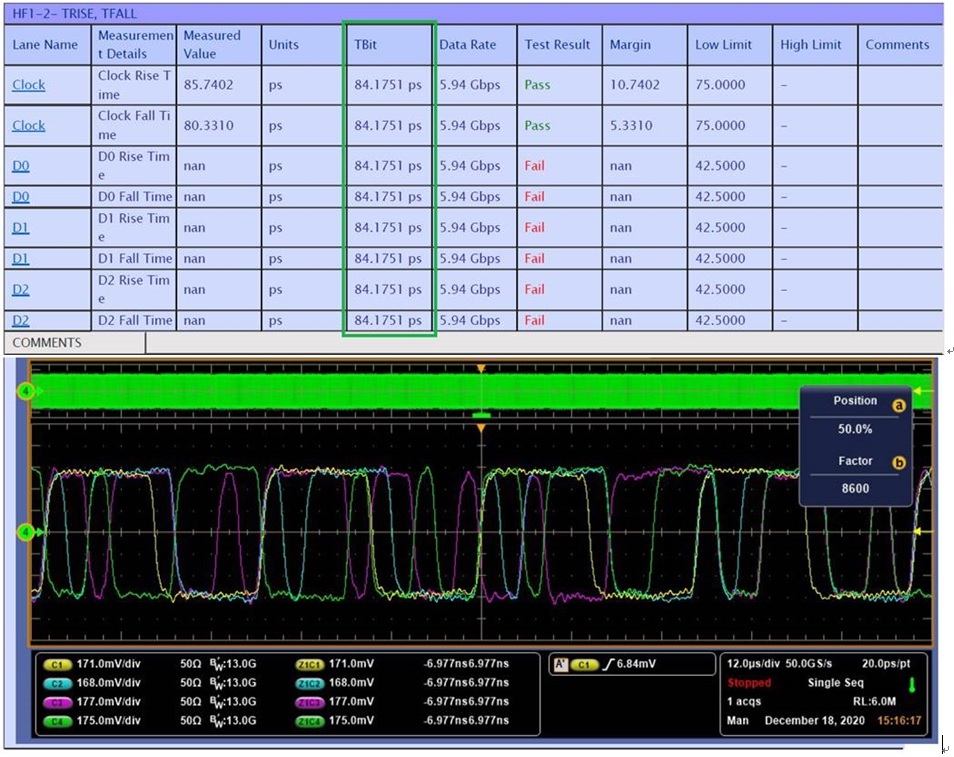

We do HDMI 2.0 SI measurement, but we found a problem, My product is Intel RKL-S platform. TBit only half compare with the CML-S pass report. We do HDMI 1.4 SI measurement and it’s pass. We do all HDMI SI measurement with RKL-S ES-2 CPU and ES-2 PCH. Does it related the CPU version? Or any setting should be checked? Please help to check, thank you.

RKL-S configuration (fail)

Intel DDI + TI SN65DP159RGZR