Other Parts Discussed in Thread: ALP, USB2ANY

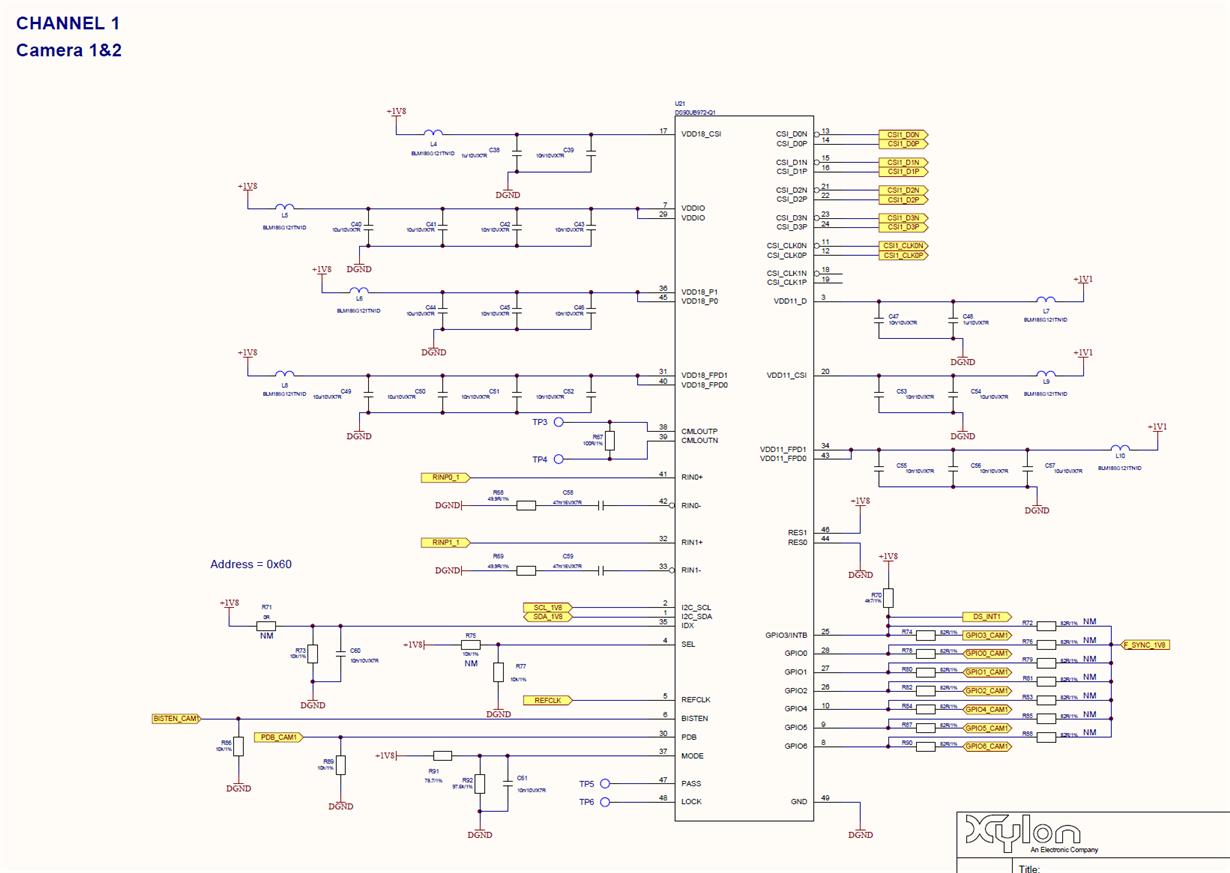

Does model (IBIS) provided for the device models capacitance seen by the oscillator that drives XIN/REFCLK pin? If not, what would be the worst case capacitance at this pin? We have a design where several DS90UB954-Q1 devices share the same clock source and we would like to know what would be capacitive load seen by clock source in this particular case. Also, if rise and fall time specification 6ns/6ns at this pin is not met (if clock edges are a bit slower, let's say 8ns), how would that influence device's performance.