When an HDMI 2.0 compatible Sink device is connected, the Soure device periodically reads the SCDC register according to the standard, but unfortunately if the Source device is turned off or the cable is disconnected in the ACK state, The Sink device keeps the SDA low. The I2C standard stipulates that the master device performs a BUS Clear operation when such a situation occurs. Is it possible to generate these 9 dummy clocks?

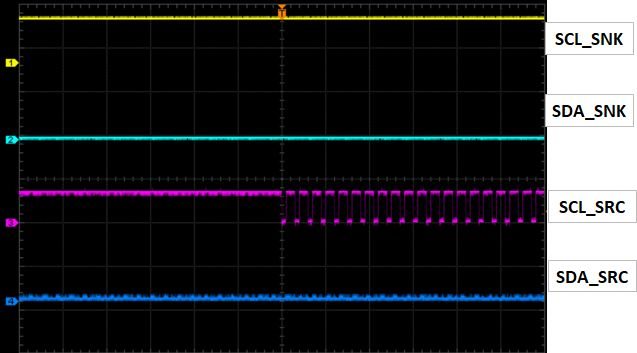

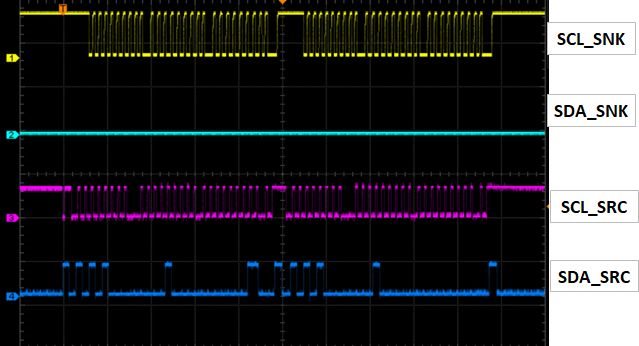

I am trying to implement this function by GPIO control, but the signal is different between SCL_SRC / SDA_SRC and SCL_SNK / SDA_SNK and I cannot implement it.

Does the "ACTIVE DDC BLOCK" depicted in the functional block diagram of the data sheet implement functions other than level conversion?