Part Number: DS90UB948-Q1

Other Parts Discussed in Thread: SN65DSI84, LMK61E0M

Hello,

We have the following configuration:

MIPI DSI => DS90UB941 => 1 single ended FPD link => DS90UB948 => LVDS screen (800x1200 at 60 fps)

PCLK = 72MHz

When using an external clock for the serialiser (DS90UB941), what is the timing tolerance in terms of pixel clock on the LVDS ?

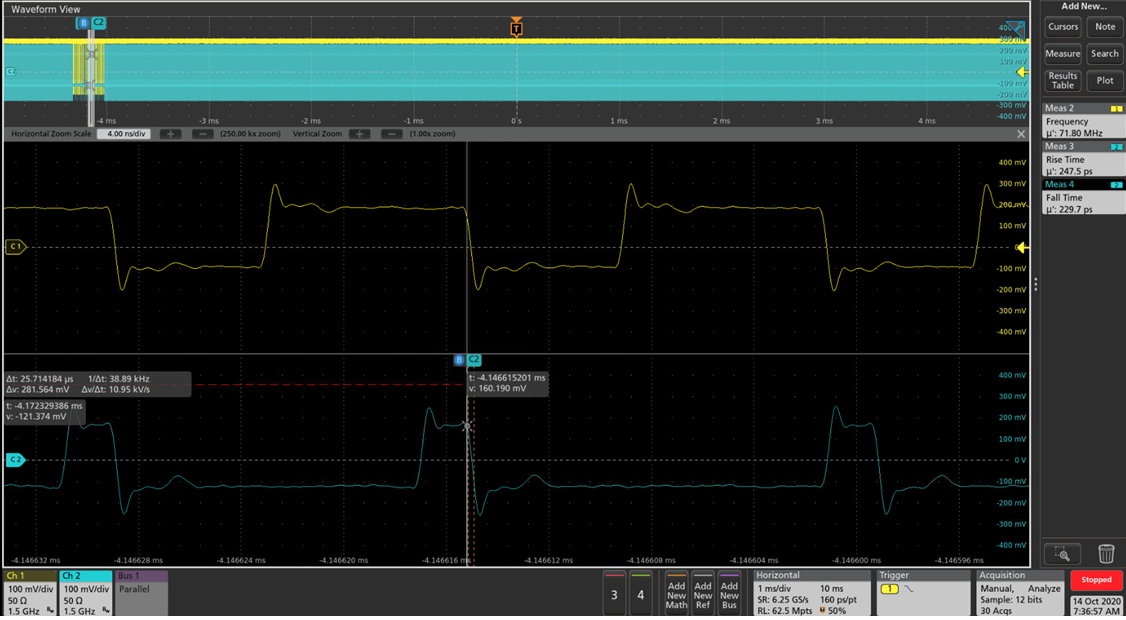

I did some measurements and i have the following (in Pixel clock):

Horizontal Front Porch / Horizontal Sync / Horizontal back porch / data

56 / 24 / 24 / 799 = 903

55 / 24 / 24 / 800 = 903

58 / 24 / 23 / 800 = 905

When doing the same measurement with the MIPI clock of the DS90UB941, i have stable timing, in line with our MIPI configuration:

72 / 24 / 24 / 800 = 920

Why do we have different timing on the Front porch, and why the timing are not stable with the external clock ?

Is it the retiming between the MIPI clock and the external clock domain ?

Is it possible to improve it ?

We also have the same behavior (screen flickering) with the SN65DSI84 (MIPI to LVDS bridge).

Thanks,

Best regards,

Alexandre