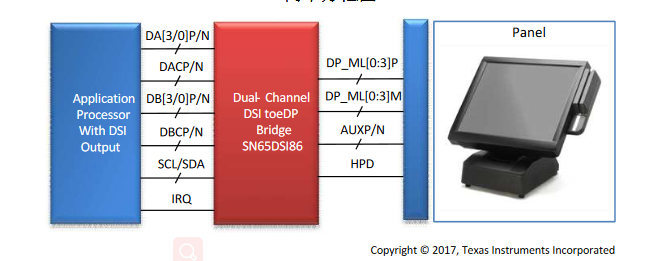

Part Number: SN65DSI86

Other Parts Discussed in Thread: TEST2,

Hi

Occasionally, the display screen abnormal phenomenon,what may be the cause?

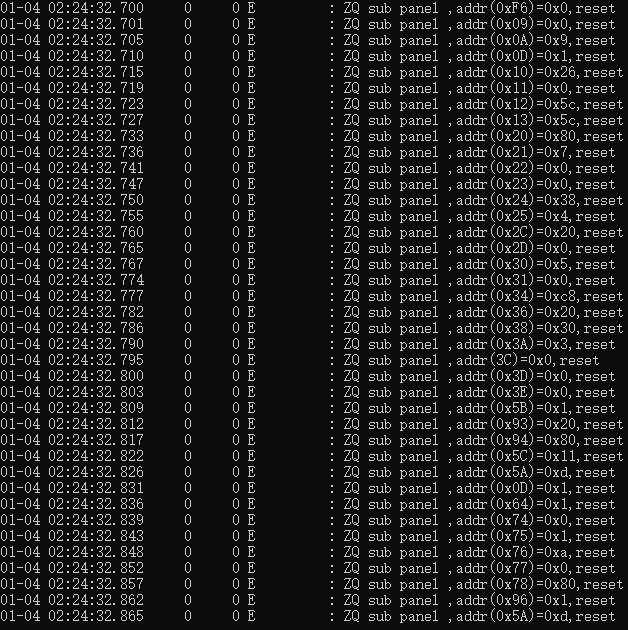

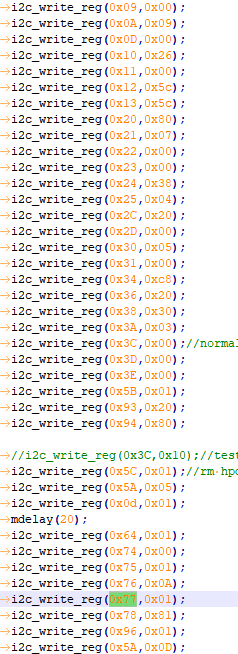

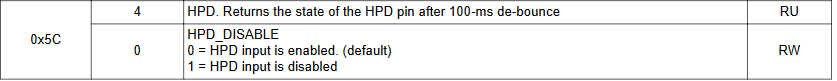

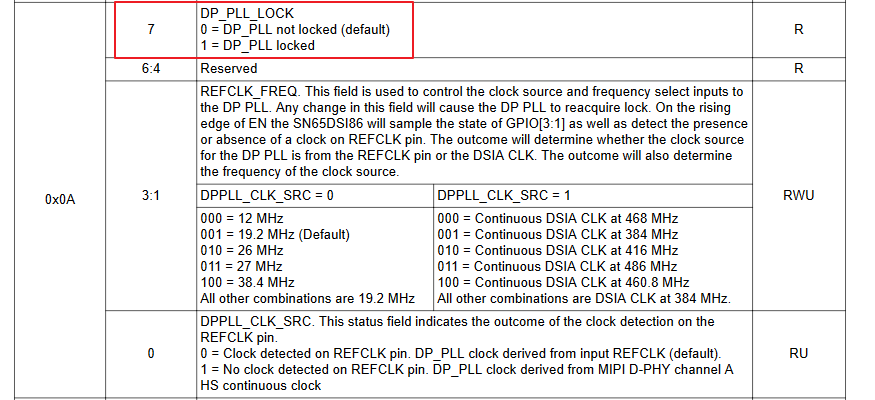

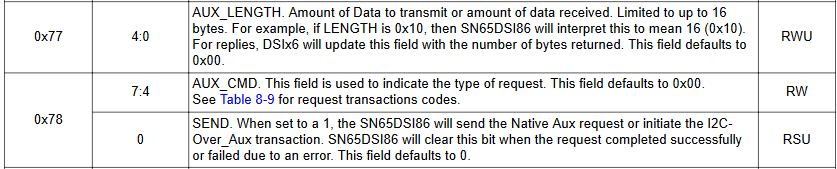

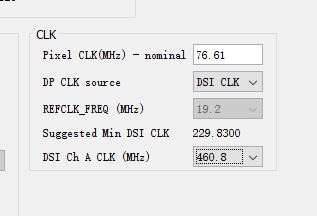

One of the phenomena is that the value that registers read is different from the value that registers write.The missing register is 0A 5C 77 78,Thanks!

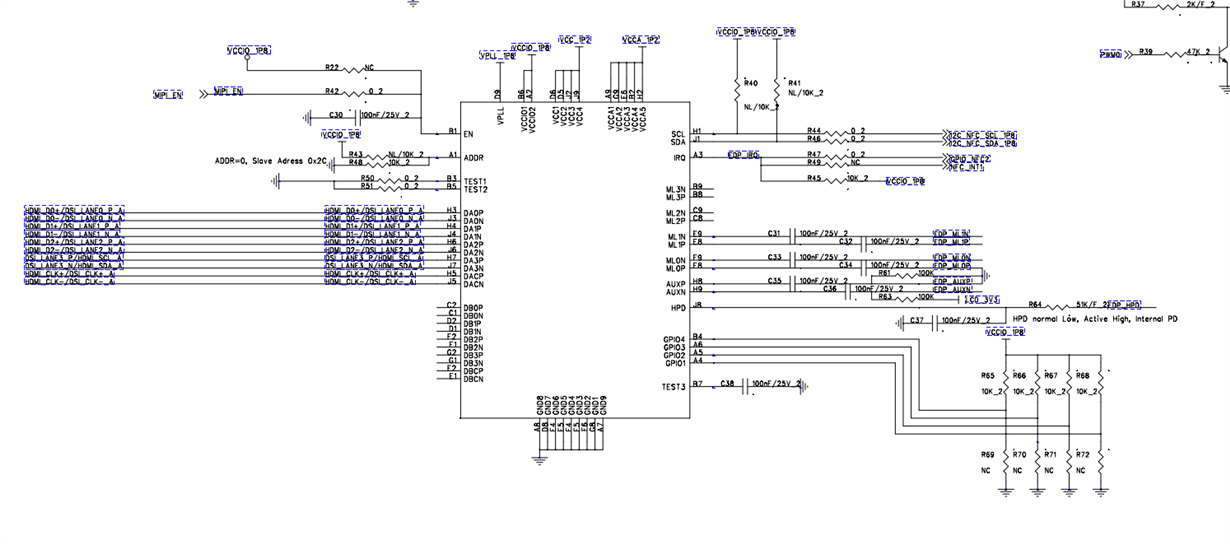

The application is the same as in the datasheet