Hello,

Our customer's application is as below:

SOC <--DSI--> ds90ub941 serializer <--FPDLINK--> ds90ub948 deserializer <--oLDI--> ds90cf366 <--RGB--> display monitor (480x240)

ds90ub941 configured CLOCK Mode 0: “FPD-Link III is generated from DSI clock. The DSI clock has to be continuous.”。

First he configured the 4 DSI data lane(by MODE_SEL0 configuration), but the display monitor couldn't appear。

And then he configured the register 0X4F and changed to 1 lane, the display could appear.

So the question is that:

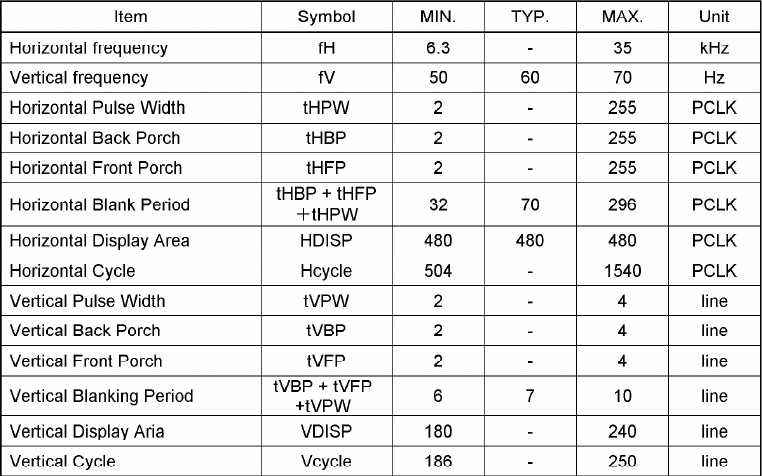

1. The datasheet described the pixel clock frequency range is 25Mhz to 105 MHz over one lane. But why the 480*240 LCD could dispaly?

2.Why the data lane is changed from 4 to 1, and the LCD could display?

Best regards

Kailyn