Part Number: DP83TD510E

Hello,

I have an question for XI input of DP83TD510E.

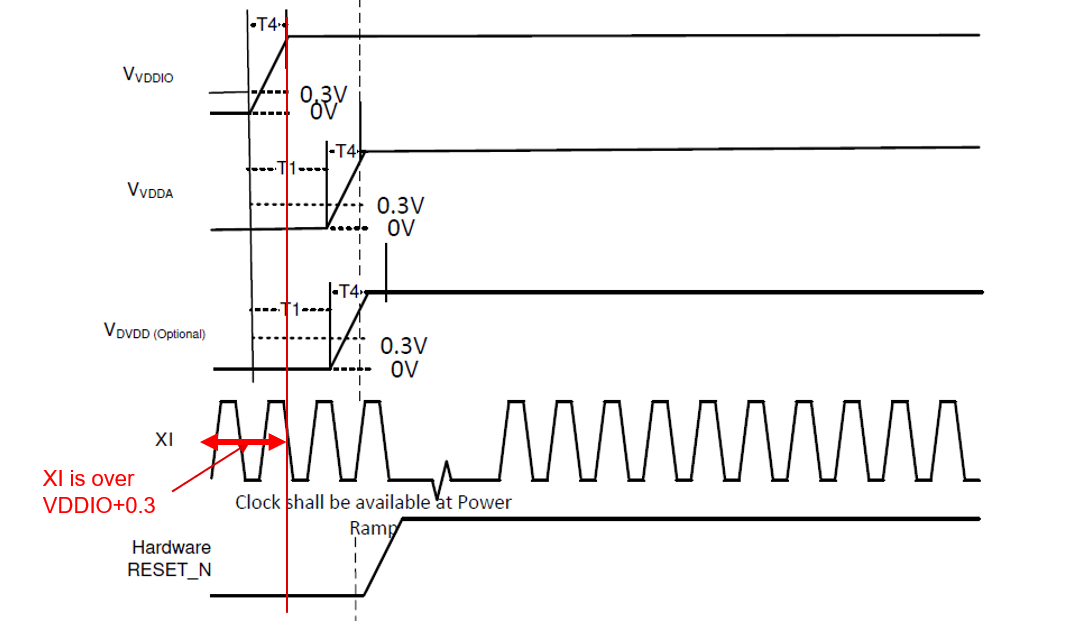

The absolute max voltage of XI input is defined as up to VDDIO+0.3V.

But in Figure 6-1 of the datasheet. XI is input before VDDIO ramp-up.

And there is a description, “Clock shall be available at Power Ramp”.

What does it mean?

Regards,

Oba