Other Parts Discussed in Thread: HALCOGEN

Hi All,

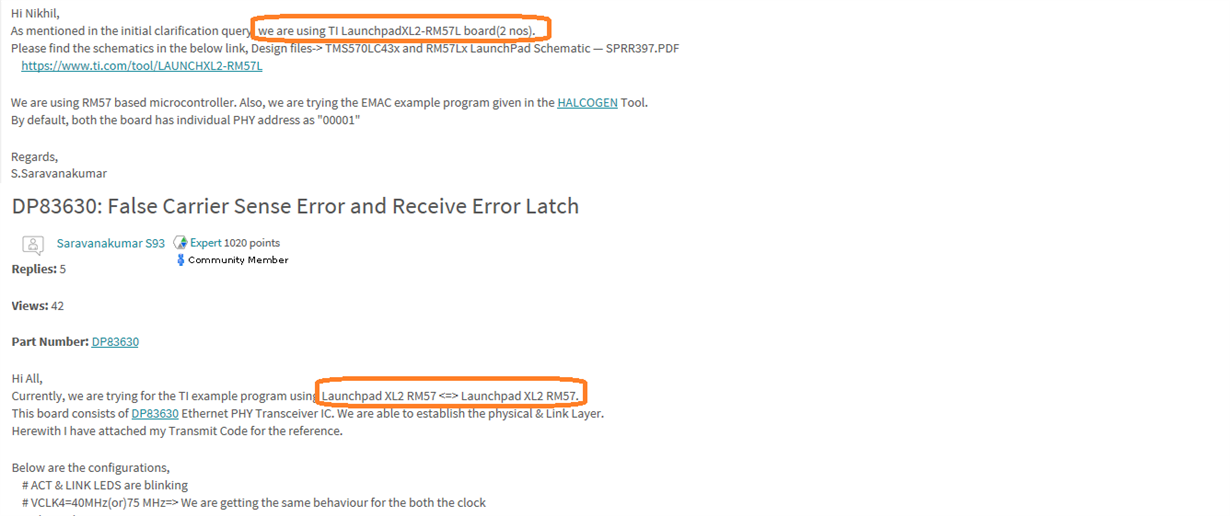

Currently, we are trying for the TI example program using Launchpad XL2 RM57 <=> Launchpad XL2 RM57.

This board consists of DP83630 Ethernet PHY Transceiver IC. We are able to establish the physical & Link Layer.

Herewith I have attached my Transmit Code for the reference.

Below are the configurations,

# ACT & LINK LEDS are blinking

# VCLK4=40MHz(or)75 MHz=> We are getting the same behaviour for the both the clock

# Channel 0

# BROADCAST addressing

# MAC ADDRESS(Point to Poin.There is no IP address configured as of now. Sending the packets in Broadcast MAC address)

# Phy address=0x01 for the both the launchpad XL2-RM57

Below are the MCU register reading status,

MACINTMASKSET 0x00000000

MACINTSTATMASKED 0x00000000

MACCONTROL 0x00000023

MACSTATUS 0x80000000

MACINVECTOR 0x00010001

MACEOIVECTOR 0x00000002

MACINTSTATRAW 0x00000000

MDIO_LINK 0x00000002

MDIO_LINKINTRAW 0x00000000

MDIO_LINKINTMASKED 0x00000000

MDIO_USERACCESS0 0x20A1CDE1

MDIO_USERPHYSEL0 0x00000000

TXINTMASKSET 0x00000001

RXINTMASKSET 0x00000001

TXINTMASKCLEAR 0x00000001

RXINTMASKCLEAR 0x00000001

TXINTSTATRAW 0x00000001

RXINTSTATRAW 0x00000001

TXINTSTATMASKED 0x00000001

RXINTSTATMASKED 0x00000001

CPGMAC_INTCONTROL 0x00000000

C0MISCEN 0x00000000

C0MISCSTA 0x00000000

Below are the PHY register(DP83630) reading status,

0x00 BMCR 0x3100

0x01 BMSR 0x78ED

0x04 ANAR 0x01E1

0x05 ANLPAR 0x41E1

0x06 ANER 0x0007

0x07 ANNPTR 0x2801

0x10 PHYSTS 0x2815

0x11 MICR 0x0000

0x12 MISR 0x2F00(First Time Read)

0x0300(Second Time Read)

0x13 PAGESEL 0x0000

0x14 FCSCR 0x00FF(First Time Read)

0x00FF(Second Time Read)

0x15 RECR 0x00FF(First Time Read)

0x00FF(Second Time Read)

0x16 PCSR 0x0100

0x17 RBR 0x0001

0x18 LEDCR 0x0000

0x19 PHYCR 0x8021

0x1A 10BTSCR 0x0804

0x1B CDCTRL1 0x0000

0x1C PHYCR2 0x0002

0x1D EDCR 0x6011

0x1F PCFCR 0x0000

As per the above register status analysis,

#We are getting the False Carrier Sense(Packet Error)/Receiver Error Latch. But, the polariy is correct.

#Even if you reread the register twice(False Carrier Counter), the register is not getting cleared.

#Even if you reread the register twice(Receive Error Counter), the register is not getting cleared.

Below are the clarifications,

# Could you please give your valuable feedback, How can we resolve the False Carrier/Receive Error Latch issue?

# Do we need to connect any external resistance as per the below link recommendation?

e2e.ti.com/.../785415

# Does any one give the Example Code/Sample Code

Thank you.

Regards,

S.Saravanakumar