Hi,

We use DS90UB933 and DS90UB934 to do a streaming media rearview mirror project.

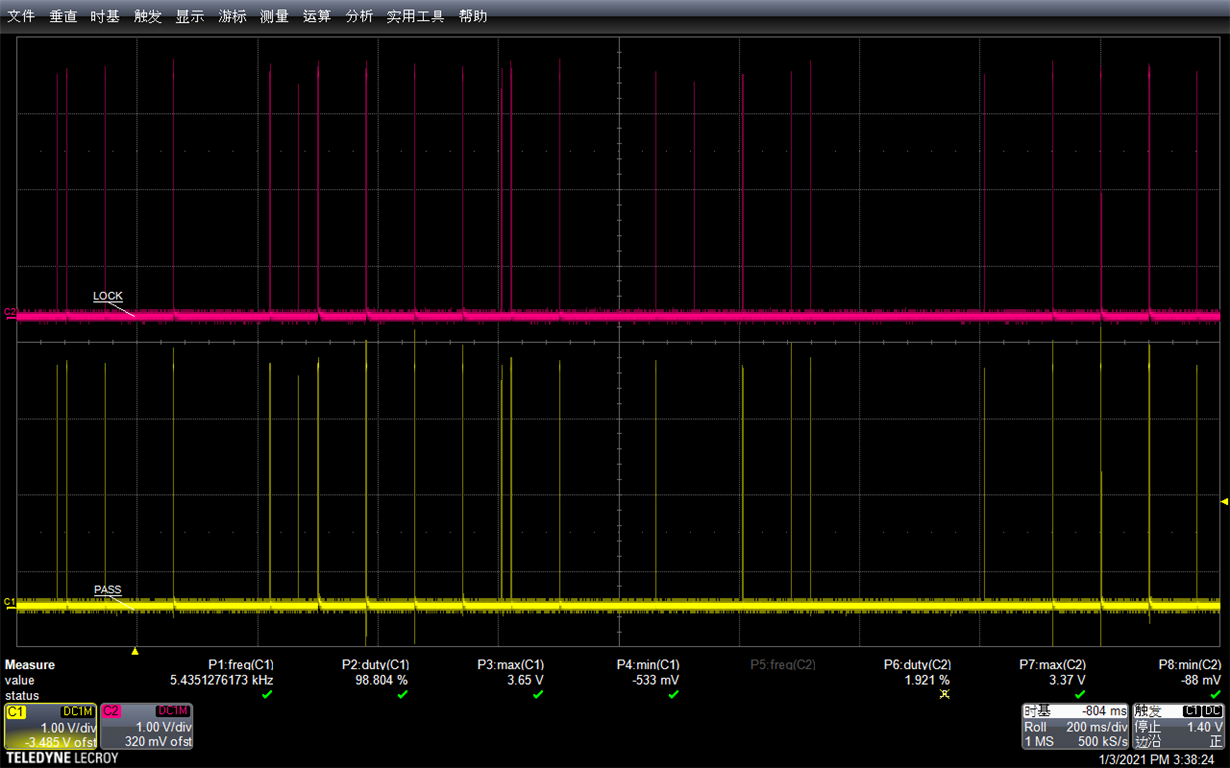

1. After the rear camera is connected, it is found that the LOCK and PASS pins of DS90UB934 output pulse signals, as shown in the figure. What is the possible cause of the failure? Where should we check?

2. The mode pin of DS90UB934 is configured with COAX RAW10, so DS90UB933 does not have this pin or register to configure COAX RAW10. How do we confirm? Is it COAX RAW10 mode just to connect DIN0 ~ DIN9 of DS90UB933 to the data line?