Part Number: DP83822H

Other Parts Discussed in Thread: TMDXICE110, AMIC110

Hi,

My customer currently make a EtherCAT Conformance Test with our DP83822H. He has the following question:

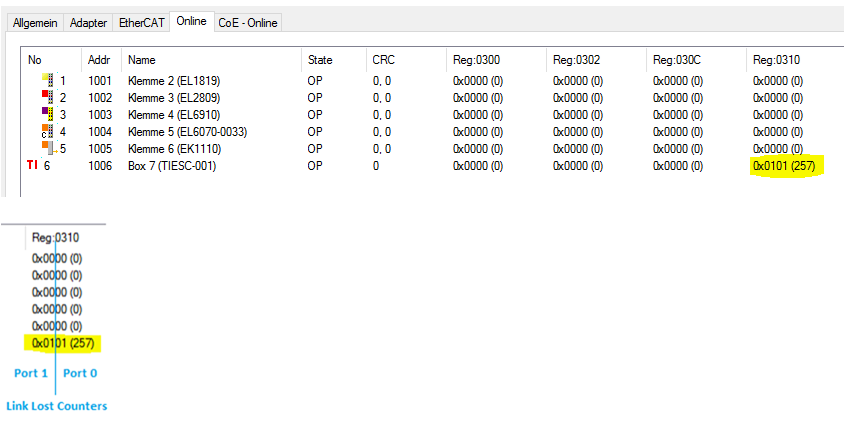

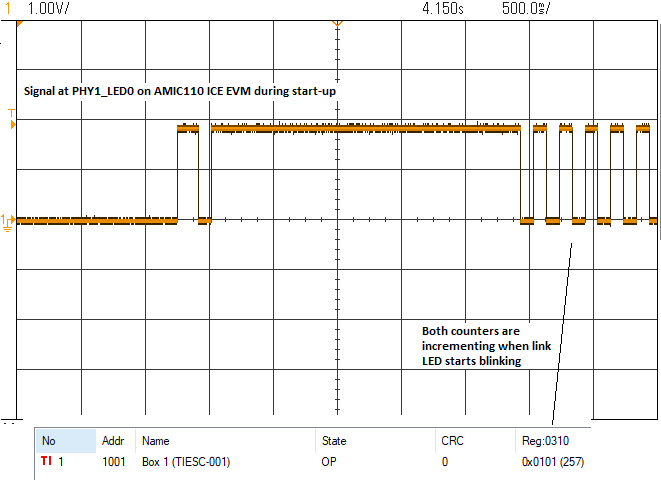

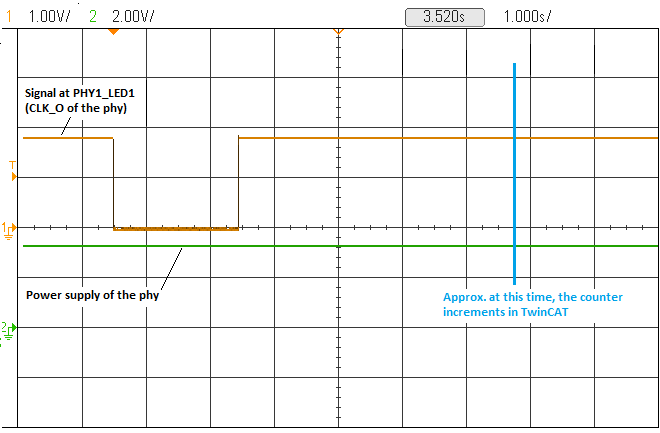

According to the test specification you have to observe some counters, which are selected accordingly in TwinCAT. The counters 'Link Lost A/B" always take the value 1 after a reset. I.e. there seems to be a short interruption after the link is established.

I can see this misbehavior on our device as well as on the AMIC board "TMDXICE110". It occurs on every reboot, regardless of whether it is a power reset or soft reset. However, the cause is unclear to me. Can you find out for me why the counters of both ports are incremented by the value '1' at each restart?

Thanks

Jan