Other Parts Discussed in Thread: AM3352,

Hello,

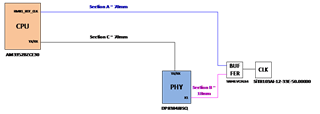

we use AM3352 and DP83848JSQ/NOPB for a Ethernet service interface.

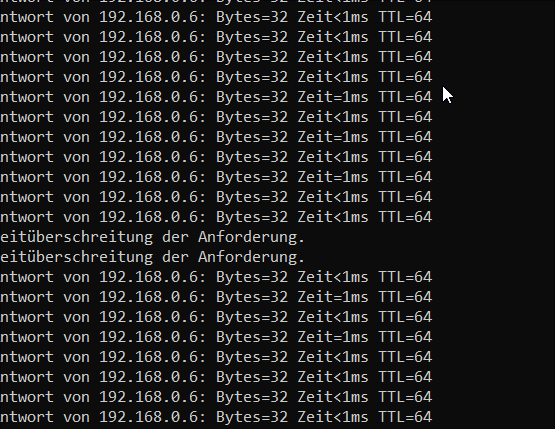

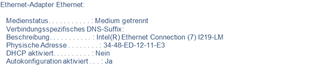

We see here Ethernet connection breaks once in a while:

Either the ping and establishing a connection does not work or everything works and suddenly it breaks.

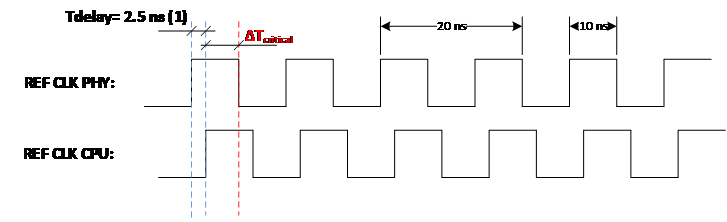

we had some EMC issues during development and had some workarounds on REF:CLK for ETH PHY. Also the clock source is in quite a distance to the Sitara. We also know that the solution with SN74LVC2G14DCK buffer is not optimal. One workaround was to increase C517 to 33pF to reduce the delay to Sitara.

With that we reduced the delay between U500 Pin 28 (DP83848JSQ/NOPB) and U100, Pin K18 (AM3352BZCE30) from 2,65ns to ~ 2ns.

PHY marking:

2021:

88A80R63

83848JSQ

2016:

49ANJKG3

83848JSQ

Is there anything else beside of the delay what may play a role here? Or is it just necessary to hold the delay under 2ns? please find the schematic and layout attached.

looking forward to your answer.

2870.Mainboard_CPU_ETH_PHY.pdf

Regards,

Alen