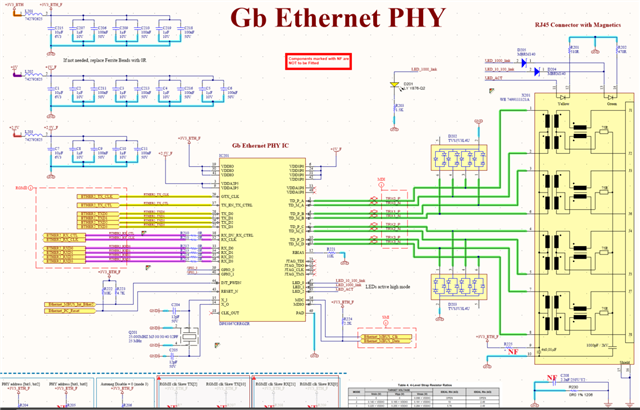

Part Number: DP83867CR

Other Parts Discussed in Thread: TIDA-00204

Hello,

We have designed a 6-layer daughter board with DP83867CRRGZ phy where we mount a SOM with a Sitara AM335x and we are experiencing some issues connecting to our local network.

We used 0R series resistors at the RGMII Rx lines as in TIDA-00204 since there is integrated 50-Ω series impedance, the Link LED is on at the RJ45 connector, but we could not see the device, no IP on the network (There are 33R series resistors on the Tx lines at the processor side on SOM). We tried 22R series resistors at the Rx lines and we noticed that we could establish connection sometimes but not always. When it connects it seems that there is no packet drop.

Could that mean there is an impedance mismatch issue on the board? What else would cause such a behavior? Is it possible some kind of startup condition with the reset signal or power to cause this problem?

Some additional info:

-Autoneg Disable = 0 (mode 3) with straps.

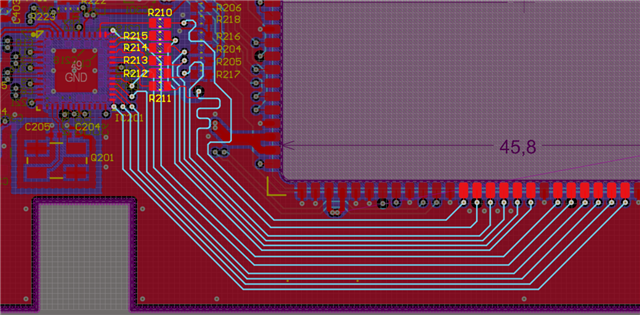

-For Stackup and track geometries, values proposed by the manufacturer where used.

-50 Ohm impedance for RGMII signals

-RJ45 with integrated magnetics used.

-All RGMII signals where routed as asymmetric striplines on layer 3 referencing Ground planes on Layers 2 and 5. Layer 4 was not used in the area under the RGMII signals.

-RGMII signals where length matched with lengths between 55 and 58mm for Rx lane and 61-64mm for Tx lane.

I am also attaching the schematic with the phy connections and a screenshot of the layout.

Thank you very much in advance.