Part Number: DS90UH949A-Q1

Hi team,

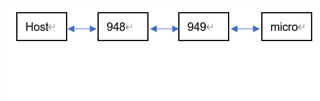

I am trying to calculate I2C latency of below system with combination of 948/949 Ser/Des.

The host needs to write 2 registers (total 2byte) of microprocessor.

I2C: 400kHz

F channel PCLK: 108.26MHz

Would you please kindly tell me how to calculate latency?

Thanks