How does the stretching and arbitration mechanism of TCA9617A work?

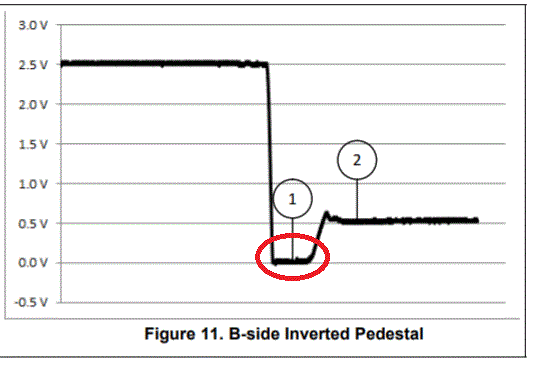

How many delay time at sequence (1)?

And why is there an offset voltage 0.5V at B side?

If there is signal interference at sequence (2), make the voltage drop to 0V then back to 0.5V, what effect will A side have at this time?

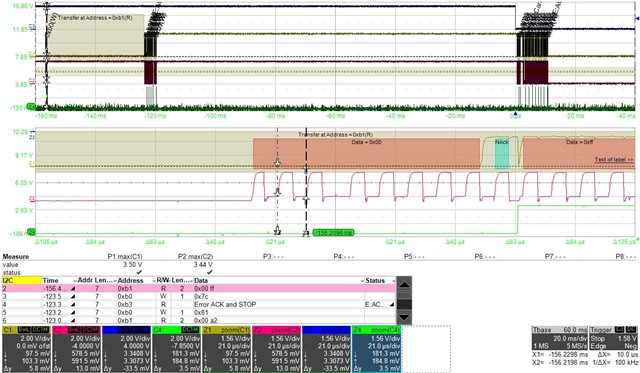

We have find when a signal interference at sequence (2), then we will loss the A side clock. The waveform show in below.

BR,

Gary