Part Number: DP83867IS

Other Parts Discussed in Thread: MIO

Hello,

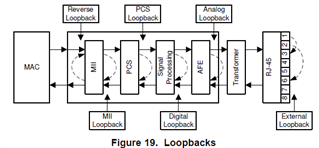

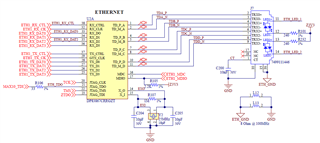

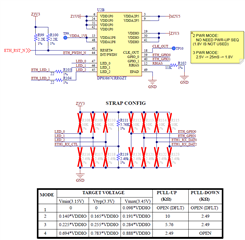

I'm having a problem; however, I'm not sure if Strap Config is not right or VDDIO has wrong voltage value. My SW guy tested with simple "ping" from another PC, he could see the receive data, but cannot transmit "ack" back. The TX side didn't work. He also tested the "Loopback" from MAC to MII (1st level) as shown below and did not see anything because of the TX side did not send anything.

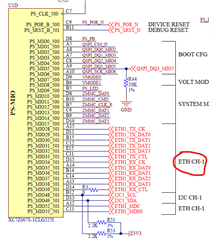

Here is the connection from my schematic. This PHY device is connected directly to Xilinx Zynq. Both devices used 3.3V for IO to eliminate extra voltage shifter device.

What did I do wrong here in HW connection? Your help is appreciated much.

Thank you.