Other Parts Discussed in Thread: DP83867ERGZ-R-EVM

Greetings,

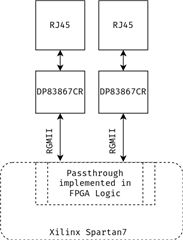

I'm interfacing DP83867CR in RGMII mode with Xilinx Spartan7 FPGA. RGMII traces on PBC are length/impedance matched without added clock delay. Inside FPGA RGMII is converted into GMII using IDDR primitives.

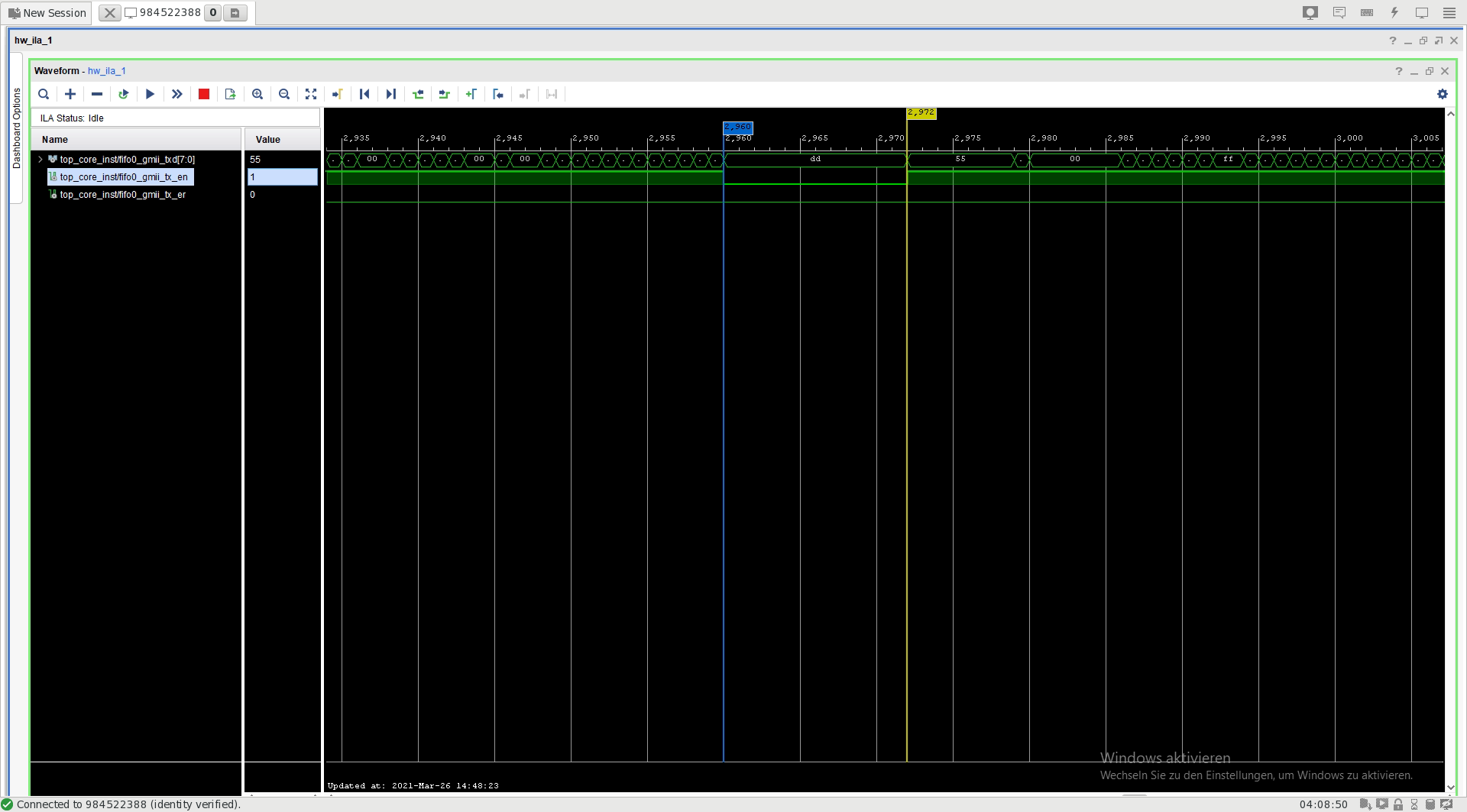

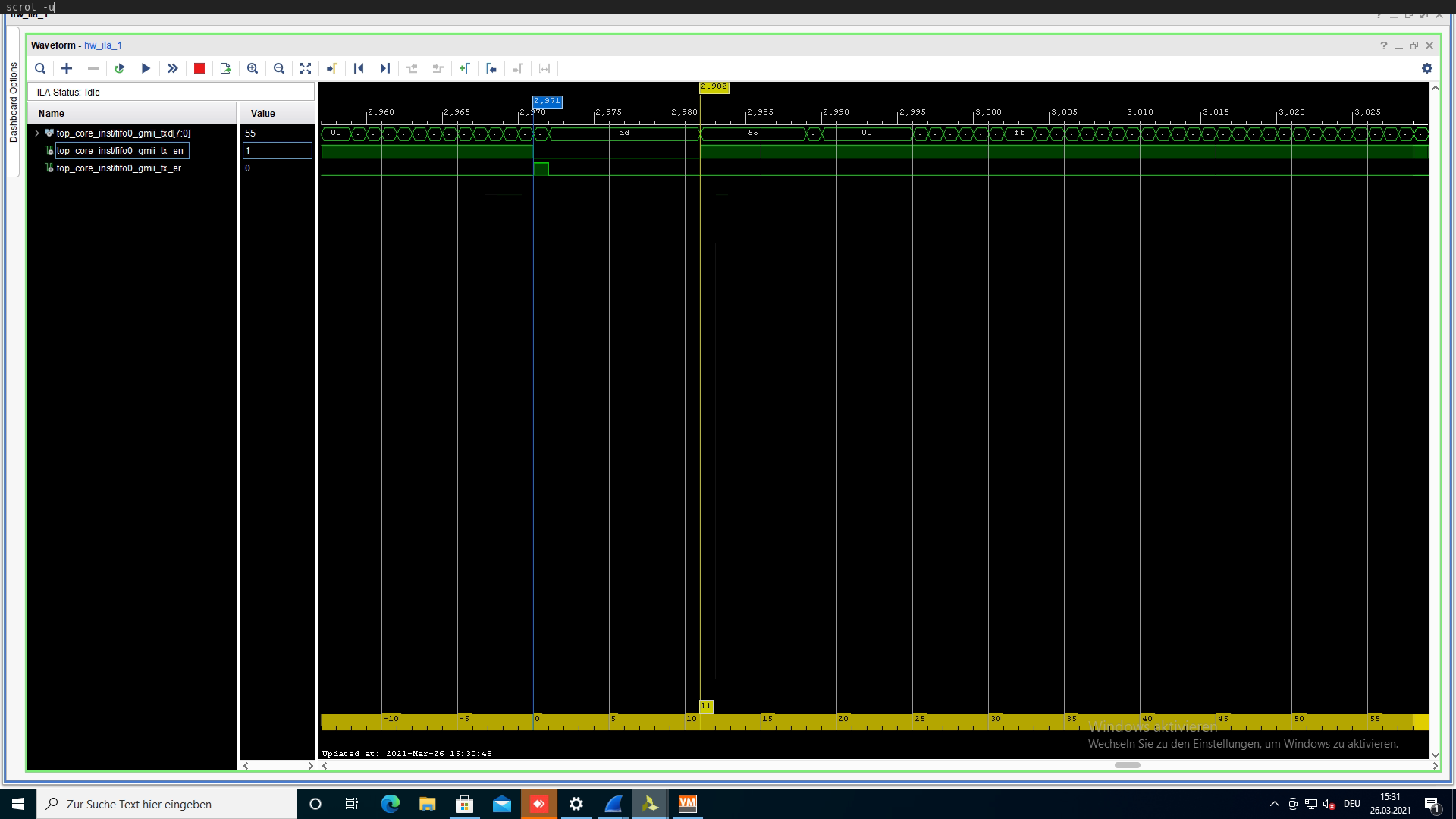

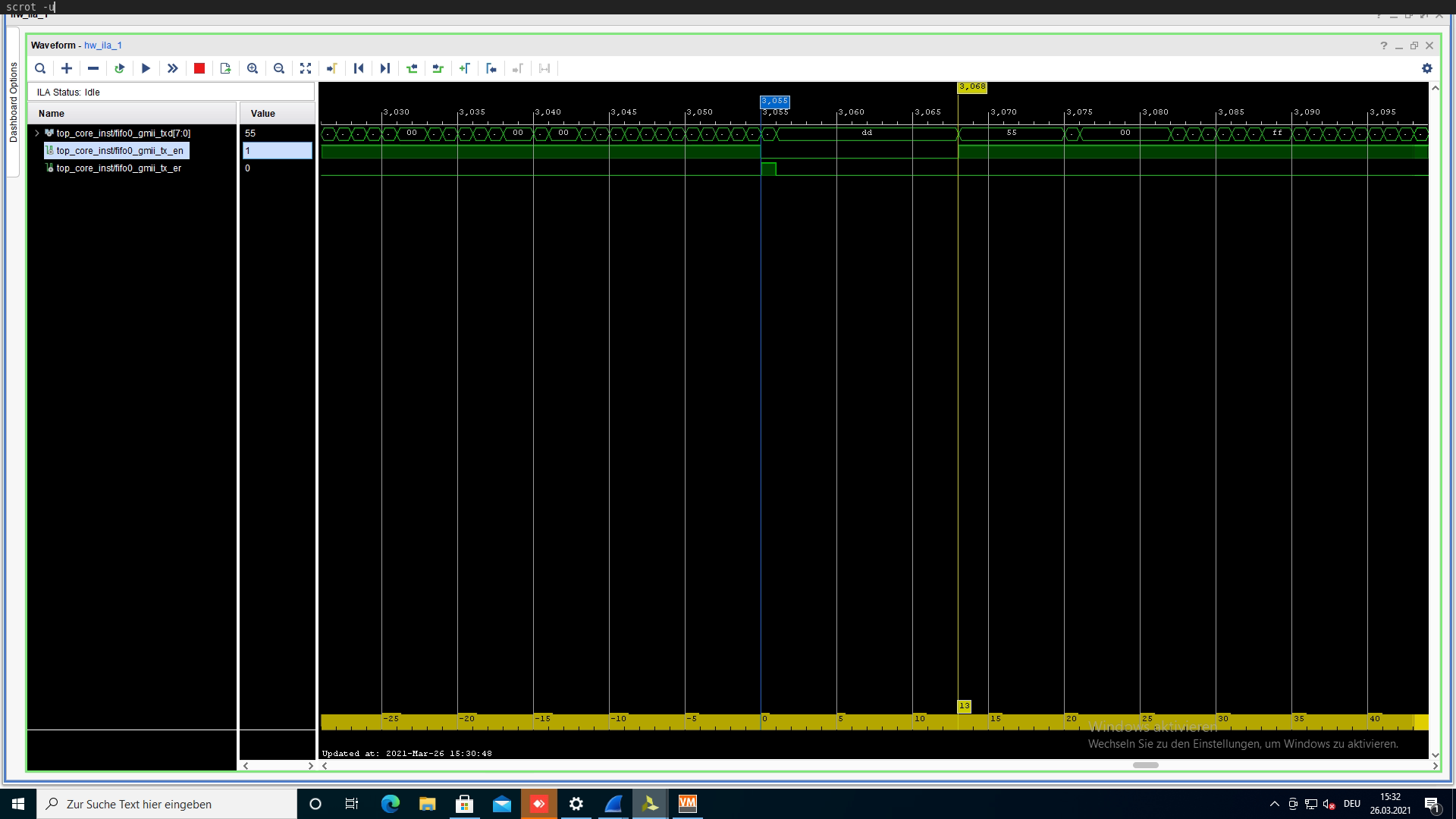

I'm expiriencing a verry strange issue, where when sending ethernet frames with even number of bytes everything works fine. In contrast when sending odd sized frames the RX_CTRL signal is behaving strangely. It can be seen in pictures below.

Picture above shows Xilinx logic analyzer with even sized frames, inter frame gap is 12 and RX_CTRL is sampled correctly.

Two pictures abowe show the same situation, just with odd sized frames. As shown gmii enable signal is deasserted before packet end, and the error signal is asserted.

Also inter frame gap is 11 cycles and 13 cycles repetitevly, never 12.

The RX clock delay is implemented with FPGA primitives and I've tried also setting various RX_CLK delays using PHY with MDIO. Also I tried delaying data and control while leaving clock in place.

Nothing really worked.

I have the same board with simmilar PHY from alternative manufacturer where I don't get those errors.

Please ask for any additional info if needed.

Thank you.

Asmir A