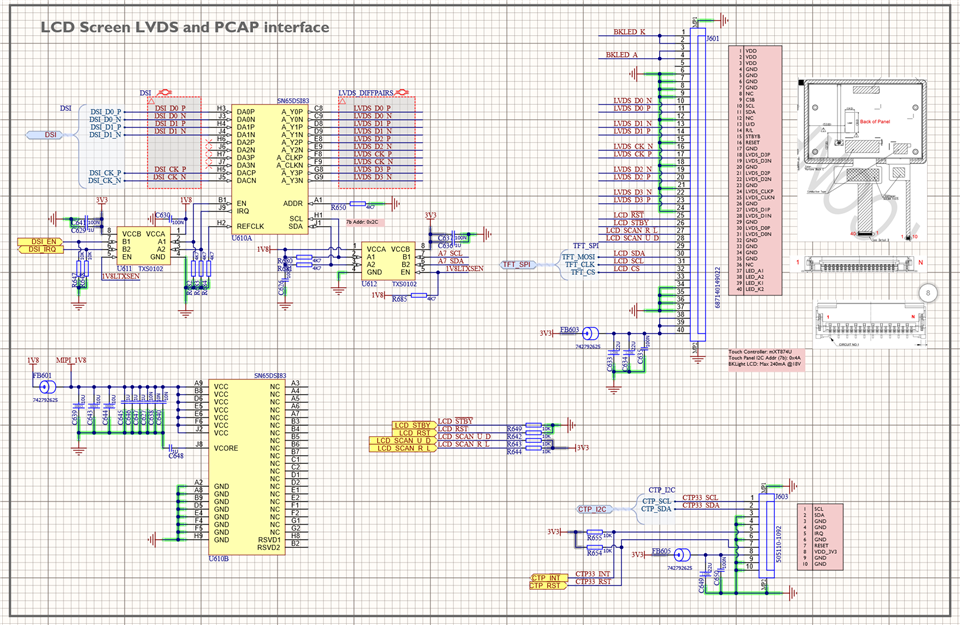

Part Number: SN65DSI83

Hi

We are using SN65DSI83 to convert DSI to LVDS. Our processor only has two DSI pairs and IO voltage is 3V3.

I was wondering if you would be able to review the schematic for us? Please see attached image

Thanking you very much in advance