Part Number: DP83822I

My boot strap is mode 3. but I read the register 0x467 bits 5:4 is mode 0.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: DP83822I

My boot strap is mode 3. but I read the register 0x467 bits 5:4 is mode 0.

Hello

Thank you for reaching out. You could copy the picture and insert as below.

On the hardware, can you please check if any of the other pin straps made and if those works.

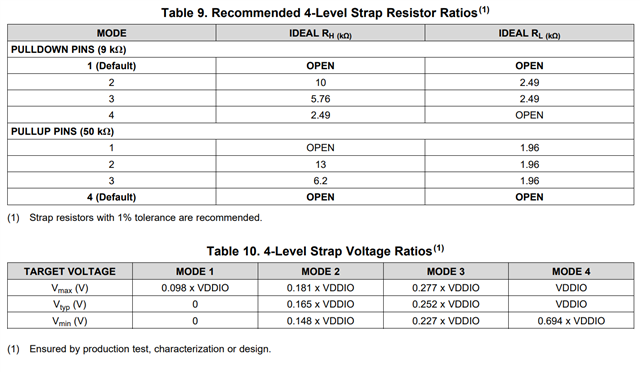

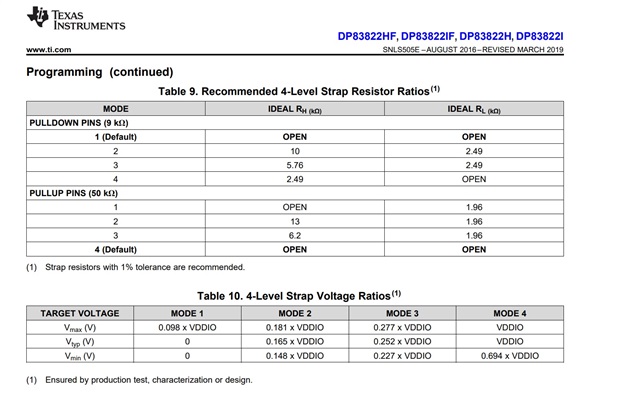

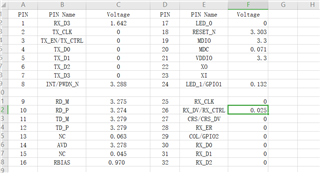

Can you please measure the voltage for the pin and the resistors values are as below.

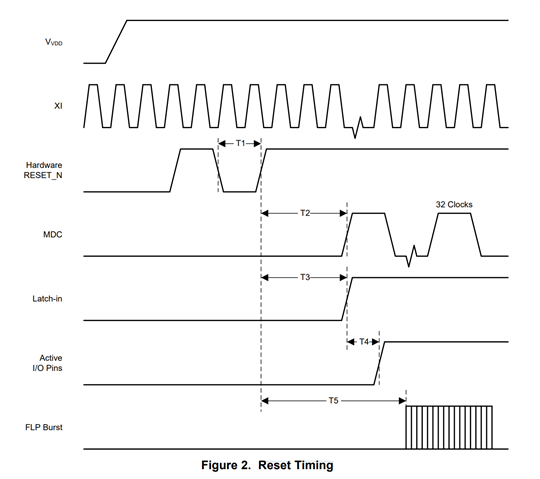

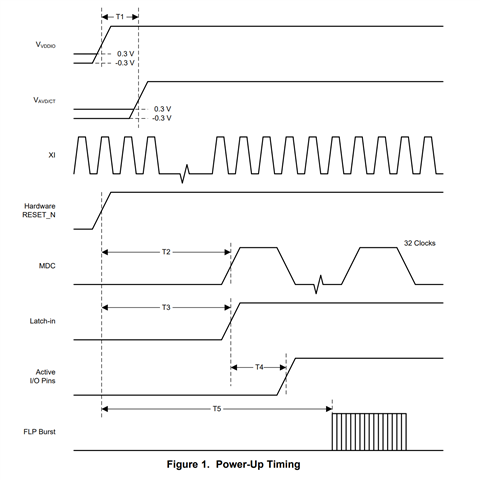

Can you please check the reset timing. If the reset is controlled by a pin, can you please do a hard reset after full boot and follow the recommended timing.

Regards,

Sreenivasa

Are you online. Can you send me your mail address. Thank you very much. I cant upload the picture, its strange.

Hello

Please use insert -> image/video file

Click upload and select the image .

I attached the file in a similar way.

Regards,

Sreenivasa

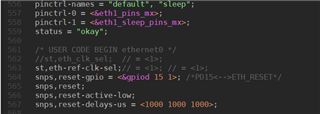

Sreenivasa : Its too easy, "upload" is grey...RX_DV choice is Mode 3. I use this source code to read address. The result is .

Sreenivasa : Its too easy, "upload" is grey...RX_DV choice is Mode 3. I use this source code to read address. The result is .

[ 18.670834] dp83822 phy reset---

[ 18.677082] dp83822 RCSR status:65

[ 18.689758] dp83822 BMCR status:3100

[ 18.734505] dp83822 BMSR status:7849

[ 18.757599] dp83822 PHYIDR1 status:2000

[ 18.812047] dp83822 PHYIDR2 status:a240

[ 18.864264] dp83822 ANAR status:1e1

[ 18.873709] random: crng init done

[ 18.879116] random: 7 urandom warning(s) missed due to ratelimiting

[ 18.915881] dp83822 ANLPAR status:0

[ 18.916612] dp83822 ANER status:4

[ 18.934837] dp83822 ANNRPTR status:2001

[ 18.953728] dp83822 ANLNPTR status:0

[ 18.969862] dp83822 CR1 status:0

[ 18.983735] dp83822 CR2 status:100

[ 19.003762] dp83822 CR3 status:1000

[ 19.022603] dp83822 REGCR status:0

[ 19.044133] dp83822 ADDAR status:0

[ 19.054226] dp83822 FLDS status:0

[ 19.083732] dp83822 PHYSTS status:1002

[ 19.100659] dp83822 PHYSCR status:108

[ 19.120782] dp83822 MISR1 status:4000

[ 19.154671] dp83822 MISR2 status:a00

[ OK ] Started Load/Save Random Seed.

[ 19.172237] dp83822 FCSCR status:0

[ 19.186545] dp83822 RECR status:0

[ 19.196933] dp83822 BISCR status:100

[ 19.223679] dp83822 RCSR status:61

[ 19.240438] dp83822 PHYCR status:8021

[ 19.251420] dp83822 10BTSCR status:10

[ 19.281339] dp83822 BICSR1 status:7d

[ 19.302077] dp83822 BICSR2 status:5ee

[ 19.321326] dp83822 CDCR status:102

[ 19.343902] dp83822 PHYRCR status:0

[ 19.360978] dp83822 COMPT status:2001

[ 19.379173] dp83822 PTPPSEL status:102

[ 19.409048] dp83822 TX_CLK status:2000

[ 19.428722] dp83822 ALCDRR1 status:0

[ 19.442053] dp83822 CDSCR status:4002

[ 19.458341] dp83822 RCSR status:61

[ 19.485407] dp83822 0x467 status:2001

[ 19.504138] dp83822 0x468 status:0

[ 19.518624] dp83822 0x463 status:a240

[ 19.540487] dp83822 0x462 status:2000

[ 19.568011] dp83822 RCSR status:61

[ 19.570520] dp83822 BMCR status:3100

[ 19.608187] dp83822 BMSR status:7849

[ 19.622726] dp83822 PHYIDR1 status:2000

[ 19.642742] dp83822 PHYIDR2 status:a240

[ 19.660822] dp83822 ANAR status:1e1

[ 19.671157] dp83822 ANLPAR status:0

[ 19.692155] dp83822 ANER status:4

[ 19.704264] dp83822 ANNRPTR status:2001

[ 19.710125] dp83822 ANLNPTR status:0

[ 19.733987] dp83822 CR1 status:0

[ 19.742844] dp83822 CR2 status:100

[ 19.756451] dp83822 CR3 status:1000

[ 19.758753] dp83822 REGCR status:401f

[ 19.776063] dp83822 ADDAR status:a1

[ 19.784027] dp83822 FLDS status:0

[ 19.787336] dp83822 PHYSTS status:2

[ 19.789505] dp83822 PHYSCR status:108

[ 19.803773] dp83822 MISR1 status:0

[ 19.806110] dp83822 MISR2 status:800

[ 19.814326] dp83822 FCSCR status:0

[ 19.816578] dp83822 RECR status:0

[ 19.824048] dp83822 BISCR status:100

[ 19.826195] dp83822 RCSR status:61

[ 19.833864] dp83822 PHYCR status:8021

[ 19.844047] dp83822 10BTSCR status:0

[ 19.846676] dp83822 BICSR1 status:7d

[ 19.853914] dp83822 BICSR2 status:5ee

[ 19.856155] dp83822 CDCR status:102

[ 19.864094] dp83822 PHYRCR status:0

[ 19.873918] dp83822 COMPT status:2001

[ 19.876073] dp83822 PTPPSEL status:102

[ 19.883996] dp83822 TX_CLK status:2000

[ 19.886409] dp83822 ALCDRR1 status:0

[ 19.893991] dp83822 CDSCR status:2

[ 19.904040] dp83822 RCSR status:61

[ 19.906127] dp83822 0x467 status:2001

[ 19.914210] dp83822 0x468 status:0

[ 19.916756] dp83822 0x463 status:a240

[ 19.923942] dp83822 0x462 status:2000

// SPDX-License-Identifier: GPL-2.0

/*

* Driver for the Texas Instruments DP83822 PHY

*

* Copyright (C) 2017 Texas Instruments Inc.

*/

#include <linux/ethtool.h>

#include <linux/etherdevice.h>

#include <linux/kernel.h>

#include <linux/mii.h>

#include <linux/module.h>

#include <linux/of.h>

#include <linux/phy.h>

#include <linux/netdevice.h>

#include <linux/delay.h>

#include <linux/gpio.h>

#include <asm/mach/map.h>

#include <asm/uaccess.h>

#include <asm/io.h>

#define DP83822_PHY_ID 0x2000a240

#define DP83825I_PHY_ID 0x2000a150

#define DP83822_DEVADDR 0x1f

#define MII_DP83822_PHYSCR 0x11

#define MII_DP83822_MISR1 0x12

#define MII_DP83822_MISR2 0x13

#define MII_DP83822_RESET_CTRL 0x1f

#define MII_DP83822_RCSR 0x17

#define DP83822_HW_RESET BIT(15)

#define DP83822_SW_RESET BIT(14)

/* PHYSCR Register Fields */

#define DP83822_PHYSCR_INT_OE BIT(0) /* Interrupt Output Enable */

#define DP83822_PHYSCR_INTEN BIT(1) /* Interrupt Enable */

/* MISR1 bits */

#define DP83822_RX_ERR_HF_INT_EN BIT(0)

#define DP83822_FALSE_CARRIER_HF_INT_EN BIT(1)

#define DP83822_ANEG_COMPLETE_INT_EN BIT(2)

#define DP83822_DUP_MODE_CHANGE_INT_EN BIT(3)

#define DP83822_SPEED_CHANGED_INT_EN BIT(4)

#define DP83822_LINK_STAT_INT_EN BIT(5)

#define DP83822_ENERGY_DET_INT_EN BIT(6)

#define DP83822_LINK_QUAL_INT_EN BIT(7)

/* MISR2 bits */

#define DP83822_JABBER_DET_INT_EN BIT(0)

#define DP83822_WOL_PKT_INT_EN BIT(1)

#define DP83822_SLEEP_MODE_INT_EN BIT(2)

#define DP83822_MDI_XOVER_INT_EN BIT(3)

#define DP83822_LB_FIFO_INT_EN BIT(4)

#define DP83822_PAGE_RX_INT_EN BIT(5)

#define DP83822_ANEG_ERR_INT_EN BIT(6)

#define DP83822_EEE_ERROR_CHANGE_INT_EN BIT(7)

/* INT_STAT1 bits */

#define DP83822_WOL_INT_EN BIT(4)

#define DP83822_WOL_INT_STAT BIT(12)

#define MII_DP83822_RXSOP1 0x04a5

#define MII_DP83822_RXSOP2 0x04a6

#define MII_DP83822_RXSOP3 0x04a7

/* WoL Registers */

#define MII_DP83822_WOL_CFG 0x04a0

#define MII_DP83822_WOL_STAT 0x04a1

#define MII_DP83822_WOL_DA1 0x04a2

#define MII_DP83822_WOL_DA2 0x04a3

#define MII_DP83822_WOL_DA3 0x04a4

/* WoL bits */

#define DP83822_WOL_MAGIC_EN BIT(0)

#define DP83822_WOL_SECURE_ON BIT(5)

#define DP83822_WOL_EN BIT(7)

#define DP83822_WOL_INDICATION_SEL BIT(8)

#define DP83822_WOL_CLR_INDICATION BIT(11)

/* RMII and Status Register(RCSR) bits */

#define DP83822_RCSR_RMII_MODE BIT(5)

#define DP83822_RCSR_RMII_CLK_SET BIT(7)

#define RCC_MP_AHB4ENSETR (0X50000A28)

#define GPIOD_BASE (0X50005000)

#define GPIO_MODER_OFFSET (0X0000)

#define GPIO_OTYPER_OFFSET (0x0004)

#define GPIO_OSPEEDR_OFFSET (0X0008)

#define GPIO_PUPDR_OFFSET (0X000C)

#define GPIO_BSRR_OFFSET (0x0018)

#define GPIO_ODR_OFFSET (0x0014)

static void __iomem *RCC_MP_AHB4ENSETR_PD;

static void __iomem *GPIO_MODER_OFFSET_PD;

static void __iomem *GPIO_OTYPER_OFFSET_PD;

static void __iomem *GPIO_OSPEEDR_OFFSET_PD;

static void __iomem *GPIO_PUPDR_OFFSET_PD;

static void __iomem *GPIO_BSRR_OFFSET_PD;

static void __iomem *GPIO_ODR_OFFSET_PD;

static int dp83822_ack_interrupt(struct phy_device *phydev)

{

int err;

err = phy_read(phydev, MII_DP83822_MISR1);

if (err < 0)

return err;

err = phy_read(phydev, MII_DP83822_MISR2);

if (err < 0)

return err;

return 0;

}

static int dp83822_set_wol(struct phy_device *phydev,

struct ethtool_wolinfo *wol)

{

struct net_device *ndev = phydev->attached_dev;

u16 value;

const u8 *mac;

if (wol->wolopts & (WAKE_MAGIC | WAKE_MAGICSECURE)) {

mac = (const u8 *)ndev->dev_addr;

if (!is_valid_ether_addr(mac))

return -EINVAL;

/* MAC addresses start with byte 5, but stored in mac[0].

* 822 PHYs store bytes 4|5, 2|3, 0|1

*/

phy_write_mmd(phydev, DP83822_DEVADDR, MII_DP83822_WOL_DA1,

(mac[1] << 8) | mac[0]);

phy_write_mmd(phydev, DP83822_DEVADDR, MII_DP83822_WOL_DA2,

(mac[3] << 8) | mac[2]);

phy_write_mmd(phydev, DP83822_DEVADDR, MII_DP83822_WOL_DA3,

(mac[5] << 8) | mac[4]);

value = phy_read_mmd(phydev, DP83822_DEVADDR,

MII_DP83822_WOL_CFG);

if (wol->wolopts & WAKE_MAGIC)

value |= DP83822_WOL_MAGIC_EN;

else

value &= ~DP83822_WOL_MAGIC_EN;

if (wol->wolopts & WAKE_MAGICSECURE) {

phy_write_mmd(phydev, DP83822_DEVADDR,

MII_DP83822_RXSOP1,

(wol->sopass[1] << 8) | wol->sopass[0]);

phy_write_mmd(phydev, DP83822_DEVADDR,

MII_DP83822_RXSOP2,

(wol->sopass[3] << 8) | wol->sopass[2]);

phy_write_mmd(phydev, DP83822_DEVADDR,

MII_DP83822_RXSOP3,

(wol->sopass[5] << 8) | wol->sopass[4]);

value |= DP83822_WOL_SECURE_ON;

} else {

value &= ~DP83822_WOL_SECURE_ON;

}

value |= (DP83822_WOL_EN | DP83822_WOL_INDICATION_SEL |

DP83822_WOL_CLR_INDICATION);

phy_write_mmd(phydev, DP83822_DEVADDR, MII_DP83822_WOL_CFG,

value);

} else {

value = phy_read_mmd(phydev, DP83822_DEVADDR,

MII_DP83822_WOL_CFG);

value &= ~DP83822_WOL_EN;

phy_write_mmd(phydev, DP83822_DEVADDR, MII_DP83822_WOL_CFG,

value);

}

return 0;

}

static void dp83822_get_wol(struct phy_device *phydev,

struct ethtool_wolinfo *wol)

{

int value;

u16 sopass_val;

wol->supported = (WAKE_MAGIC | WAKE_MAGICSECURE);

wol->wolopts = 0;

value = phy_read_mmd(phydev, DP83822_DEVADDR, MII_DP83822_WOL_CFG);

if (value & DP83822_WOL_MAGIC_EN)

wol->wolopts |= WAKE_MAGIC;

if (value & DP83822_WOL_SECURE_ON) {

sopass_val = phy_read_mmd(phydev, DP83822_DEVADDR,

MII_DP83822_RXSOP1);

wol->sopass[0] = (sopass_val & 0xff);

wol->sopass[1] = (sopass_val >> 8);

sopass_val = phy_read_mmd(phydev, DP83822_DEVADDR,

MII_DP83822_RXSOP2);

wol->sopass[2] = (sopass_val & 0xff);

wol->sopass[3] = (sopass_val >> 8);

sopass_val = phy_read_mmd(phydev, DP83822_DEVADDR,

MII_DP83822_RXSOP3);

wol->sopass[4] = (sopass_val & 0xff);

wol->sopass[5] = (sopass_val >> 8);

wol->wolopts |= WAKE_MAGICSECURE;

}

/* WoL is not enabled so set wolopts to 0 */

if (!(value & DP83822_WOL_EN))

wol->wolopts = 0;

}

static int dp83822_config_intr(struct phy_device *phydev)

{

int misr_status;

int physcr_status;

int err;

if (phydev->interrupts == PHY_INTERRUPT_ENABLED) {

misr_status = phy_read(phydev, MII_DP83822_MISR1);

if (misr_status < 0)

return misr_status;

misr_status |= (DP83822_RX_ERR_HF_INT_EN |

DP83822_FALSE_CARRIER_HF_INT_EN |

DP83822_ANEG_COMPLETE_INT_EN |

DP83822_DUP_MODE_CHANGE_INT_EN |

DP83822_SPEED_CHANGED_INT_EN |

DP83822_LINK_STAT_INT_EN |

DP83822_ENERGY_DET_INT_EN |

DP83822_LINK_QUAL_INT_EN);

err = phy_write(phydev, MII_DP83822_MISR1, misr_status);

if (err < 0)

return err;

misr_status = phy_read(phydev, MII_DP83822_MISR2);

if (misr_status < 0)

return misr_status;

misr_status |= (DP83822_JABBER_DET_INT_EN |

DP83822_WOL_PKT_INT_EN |

DP83822_SLEEP_MODE_INT_EN |

DP83822_MDI_XOVER_INT_EN |

DP83822_LB_FIFO_INT_EN |

DP83822_PAGE_RX_INT_EN |

DP83822_ANEG_ERR_INT_EN |

DP83822_EEE_ERROR_CHANGE_INT_EN);

err = phy_write(phydev, MII_DP83822_MISR2, misr_status);

if (err < 0)

return err;

physcr_status = phy_read(phydev, MII_DP83822_PHYSCR);

if (physcr_status < 0)

return physcr_status;

physcr_status |= DP83822_PHYSCR_INT_OE | DP83822_PHYSCR_INTEN;

} else {

err = phy_write(phydev, MII_DP83822_MISR1, 0);

if (err < 0)

return err;

err = phy_write(phydev, MII_DP83822_MISR1, 0);

if (err < 0)

return err;

physcr_status = phy_read(phydev, MII_DP83822_PHYSCR);

if (physcr_status < 0)

return physcr_status;

physcr_status &= ~DP83822_PHYSCR_INTEN;

}

return phy_write(phydev, MII_DP83822_PHYSCR, physcr_status);

}

static int gpiod15_reset(void)

{

u32 val = 0;

printk(KERN_NOTICE "dp83822 gpiod15_reset---");

RCC_MP_AHB4ENSETR_PD = ioremap(RCC_MP_AHB4ENSETR, 4);

GPIO_MODER_OFFSET_PD = ioremap((GPIOD_BASE + GPIO_MODER_OFFSET), 4);

GPIO_OTYPER_OFFSET_PD = ioremap((GPIOD_BASE + GPIO_OTYPER_OFFSET), 4);

GPIO_OSPEEDR_OFFSET_PD = ioremap((GPIOD_BASE + GPIO_OSPEEDR_OFFSET), 4);

GPIO_PUPDR_OFFSET_PD = ioremap((GPIOD_BASE + GPIO_PUPDR_OFFSET), 4);

GPIO_BSRR_OFFSET_PD = ioremap((GPIOD_BASE + GPIO_BSRR_OFFSET), 4);

GPIO_ODR_OFFSET_PD = ioremap((GPIOD_BASE + GPIO_ODR_OFFSET), 4);

//enable PD clk

val = readl(RCC_MP_AHB4ENSETR_PD);

val &= ~(0X1 << 3);

val |= (0X1 << 3);

writel(val, RCC_MP_AHB4ENSETR_PD);

val = readl(RCC_MP_AHB4ENSETR_PD);

printk(KERN_NOTICE "dp83822 RCC_MP_AHB4ENSETR_PD:%x", val);

//output mode

val = readl(GPIO_MODER_OFFSET_PD);

val &= ~(0X3 << 15);

val |= (0X1 << 15);

writel(val, GPIO_MODER_OFFSET_PD);

val = readl(GPIO_MODER_OFFSET_PD);

printk(KERN_NOTICE "dp83822 GPIO_MODER_OFFSET_PD:%x", val);

//Output push pull

val = readl(GPIO_OTYPER_OFFSET_PD);

val &= ~(0X1 << 15);

writel(val, GPIO_OTYPER_OFFSET_PD);

val = readl(GPIO_OTYPER_OFFSET_PD);

printk(KERN_NOTICE "dp83822 GPIO_OTYPER_OFFSET_PD:%x", val);

//high speed

val = readl(GPIO_OSPEEDR_OFFSET_PD);

val &= ~(0X3 << 15);

val |= (0x2 << 15);

writel(val, GPIO_OSPEEDR_OFFSET_PD);

val = readl(GPIO_OSPEEDR_OFFSET_PD);

printk(KERN_NOTICE "dp83822 GPIO_OSPEEDR_OFFSET_PD:%x", val);

//pull up

val = readl(GPIO_PUPDR_OFFSET_PD);

val &= ~(0X3 << 15);

val |= (0x1 << 15);

writel(val, GPIO_PUPDR_OFFSET_PD);

val = readl(GPIO_PUPDR_OFFSET_PD);

printk(KERN_NOTICE "dp83822 GPIO_PUPDR_OFFSET_PD:%x", val);

//default high

val = readl(GPIO_BSRR_OFFSET_PD);

val |= (0x1 << 15);

writel(val, GPIO_BSRR_OFFSET_PD);

val = readl(GPIO_ODR_OFFSET_PD);

val |= (0x1 << 15);

writel(val, GPIO_ODR_OFFSET_PD);

val = readl(GPIO_ODR_OFFSET_PD);

printk(KERN_NOTICE "dp83822 high GPIO_ODR_OFFSET_PD:%x", val);

//reset: set it to low

udelay(20);

val = readl(GPIO_BSRR_OFFSET_PD);

val &= ~(0x1 << 15);

writel(val, GPIO_BSRR_OFFSET_PD);

val = readl(GPIO_ODR_OFFSET_PD);

val &= ~(0x1 << 15);

writel(val, GPIO_ODR_OFFSET_PD);

val = readl(GPIO_ODR_OFFSET_PD);

printk(KERN_NOTICE "dp83822 low GPIO_ODR_OFFSET_PD:%x", val);

mdelay(40);

//reset: set it to high

val = readl(GPIO_BSRR_OFFSET_PD);

val |= (0x1 << 15);

writel(val, GPIO_BSRR_OFFSET_PD);

val = readl(GPIO_ODR_OFFSET_PD);

val |= (0x1 << 15);

writel(val, GPIO_ODR_OFFSET_PD);

val = readl(GPIO_ODR_OFFSET_PD);

printk(KERN_NOTICE "dp83822 high GPIO_ODR_OFFSET_PD:%x", val);

//free iomem

iounmap(GPIO_ODR_OFFSET_PD);

iounmap(GPIO_MODER_OFFSET_PD);

iounmap(GPIO_OTYPER_OFFSET_PD);

iounmap(GPIO_OSPEEDR_OFFSET_PD);

iounmap(GPIO_PUPDR_OFFSET_PD);

iounmap(GPIO_BSRR_OFFSET_PD);

iounmap(RCC_MP_AHB4ENSETR_PD);

return 0;

}

static int dp83822_config_rmii(struct phy_device *phydev)

{

struct dp83822_private *dp83822 = phydev->priv;

int err;

int status;

//gpiod15_reset();

status = phy_read(phydev, MII_DP83822_RCSR);

printk(KERN_NOTICE "dp83822 RCSR status:%x", status);

if(status < 0)

{

return status;

}

/*

status |= DP83822_RCSR_RMII_MODE | DP83822_RCSR_RMII_CLK_SET;

err = phy_write(phydev, MII_DP83822_RCSR, status);

if(err < 0)

return err;

*/

status = phy_read(phydev, 0);

printk(KERN_NOTICE "dp83822 BMCR status:%x", status);

/*

status = phy_read(phydev, 0x16);

printk(KERN_NOTICE "dp83822 BISCR status:%x", status);

status |= (1<<3);

err = phy_write(phydev, 0x16, status);

status = phy_read(phydev, 0x16);

printk(KERN_NOTICE "dp83822 BISCR status:%x", status);

*/

status = phy_read(phydev, 1);

printk(KERN_NOTICE "dp83822 BMSR status:%x", status);

status = phy_read(phydev, 2);

printk(KERN_NOTICE "dp83822 PHYIDR1 status:%x", status);

status = phy_read(phydev, 3);

printk(KERN_NOTICE "dp83822 PHYIDR2 status:%x", status);

status = phy_read(phydev, 4);

printk(KERN_NOTICE "dp83822 ANAR status:%x", status);

status = phy_read(phydev, 5);

printk(KERN_NOTICE "dp83822 ANLPAR status:%x", status);

status = phy_read(phydev, 6);

printk(KERN_NOTICE "dp83822 ANER status:%x", status);

status = phy_read(phydev, 7);

printk(KERN_NOTICE "dp83822 ANNRPTR status:%x", status);

status = phy_read(phydev, 8);

printk(KERN_NOTICE "dp83822 ANLNPTR status:%x", status);

status = phy_read(phydev, 9);

printk(KERN_NOTICE "dp83822 CR1 status:%x", status);

status = phy_read(phydev, 0xa);

printk(KERN_NOTICE "dp83822 CR2 status:%x", status);

status = phy_read(phydev, 0xb);

printk(KERN_NOTICE "dp83822 CR3 status:%x", status);

status = phy_read(phydev, 0xd);

printk(KERN_NOTICE "dp83822 REGCR status:%x", status);

status = phy_read(phydev, 0xe);

printk(KERN_NOTICE "dp83822 ADDAR status:%x", status);

status = phy_read(phydev, 0xf);

printk(KERN_NOTICE "dp83822 FLDS status:%x", status);

status = phy_read(phydev, 0x10);

printk(KERN_NOTICE "dp83822 PHYSTS status:%x", status);

status = phy_read(phydev, 0x11);

printk(KERN_NOTICE "dp83822 PHYSCR status:%x", status);

status = phy_read(phydev, 0x12);

printk(KERN_NOTICE "dp83822 MISR1 status:%x", status);

status = phy_read(phydev, 0x13);

printk(KERN_NOTICE "dp83822 MISR2 status:%x", status);

status = phy_read(phydev, 0x14);

printk(KERN_NOTICE "dp83822 FCSCR status:%x", status);

status = phy_read(phydev, 0x15);

printk(KERN_NOTICE "dp83822 RECR status:%x", status);

status = phy_read(phydev, 0x16);

printk(KERN_NOTICE "dp83822 BISCR status:%x", status);

status = phy_read(phydev, 0x17);

printk(KERN_NOTICE "dp83822 RCSR status:%x", status);

status = phy_read(phydev, 0x19);

printk(KERN_NOTICE "dp83822 PHYCR status:%x", status);

status = phy_read(phydev, 0x1a);

printk(KERN_NOTICE "dp83822 10BTSCR status:%x", status);

status = phy_read(phydev, 0x1b);

printk(KERN_NOTICE "dp83822 BICSR1 status:%x", status);

status = phy_read(phydev, 0x1c);

printk(KERN_NOTICE "dp83822 BICSR2 status:%x", status);

status = phy_read(phydev, 0x1e);

printk(KERN_NOTICE "dp83822 CDCR status:%x", status);

status = phy_read(phydev, 0x1f);

printk(KERN_NOTICE "dp83822 PHYRCR status:%x", status);

status = phy_read(phydev, 0x27);

printk(KERN_NOTICE "dp83822 COMPT status:%x", status);

status = phy_read(phydev, 0x3e);

printk(KERN_NOTICE "dp83822 PTPPSEL status:%x", status);

status = phy_read(phydev, 0x42);

printk(KERN_NOTICE "dp83822 TX_CLK status:%x", status);

status = phy_read(phydev, 0x155);

printk(KERN_NOTICE "dp83822 ALCDRR1 status:%x", status);

status = phy_read(phydev, 0x170);

printk(KERN_NOTICE "dp83822 CDSCR status:%x", status);

status = phy_read(phydev, MII_DP83822_RCSR);

printk(KERN_NOTICE "dp83822 RCSR status:%x", status);

status = phy_read(phydev, 0x467);

printk(KERN_NOTICE "dp83822 0x467 status:%x", status);

status = phy_read(phydev, 0x468);

printk(KERN_NOTICE "dp83822 0x468 status:%x", status);

status = phy_read(phydev, 0x463);

printk(KERN_NOTICE "dp83822 0x463 status:%x", status);

status = phy_read(phydev, 0x462);

printk(KERN_NOTICE "dp83822 0x462 status:%x", status);

/*

if(status == 0x2000)

{

status = 0x4300;

printk(KERN_NOTICE "dp83822 write 0x462 status:%x", status);

err = phy_write(phydev, 0x462, status);

if(err < 0)

{

printk(KERN_NOTICE "dp83822 write0x462 err:%d", err);

return err;

}

status = phy_read(phydev, 0x462);

printk(KERN_NOTICE "dp83822 after write 0x462 status:%x", status);

}

*/

/*

status = phy_read(phydev, 0x461);

printk(KERN_NOTICE "dp83822 0x461 status:%x", status);

status = phy_read(phydev, 0x16);

printk(KERN_NOTICE "dp83822 0x16 status:%x", status);

status &= ~0x1;

status |= 0x4;

err = phy_write(phydev, 0x16, status);

status = phy_read(phydev, 0x16);

printk(KERN_NOTICE "dp83822 after write 0x1, 0x16 status:%x", status);

*/

return 0;

}

static int dp83822_config_init(struct phy_device *phydev)

{

int value, err;

err = dp83822_config_rmii(phydev);

if(err < 0)

return err;

value = DP83822_WOL_MAGIC_EN | DP83822_WOL_SECURE_ON | DP83822_WOL_EN;

return phy_write_mmd(phydev, DP83822_DEVADDR, MII_DP83822_WOL_CFG,

value);

}

static int dp83822_phy_reset(struct phy_device *phydev)

{

int err;

printk(KERN_NOTICE "dp83822 phy reset---");

err = phy_write(phydev, MII_DP83822_RESET_CTRL, DP83822_HW_RESET);

if (err < 0)

return err;

dp83822_config_init(phydev);

return 0;

}

static int dp83822_suspend(struct phy_device *phydev)

{

int value;

value = phy_read_mmd(phydev, DP83822_DEVADDR, MII_DP83822_WOL_CFG);

if (!(value & DP83822_WOL_EN))

genphy_suspend(phydev);

return 0;

}

static int dp83822_resume(struct phy_device *phydev)

{

int value;

genphy_resume(phydev);

value = phy_read_mmd(phydev, DP83822_DEVADDR, MII_DP83822_WOL_CFG);

phy_write_mmd(phydev, DP83822_DEVADDR, MII_DP83822_WOL_CFG, value |

DP83822_WOL_CLR_INDICATION);

return 0;

}

#define DP83822_PHY_DRIVER(_id, _name) \

{ \

PHY_ID_MATCH_MODEL(_id), \

.name = (_name), \

/* PHY_BASIC_FEATURES */ \

.soft_reset = dp83822_phy_reset, \

.config_init = dp83822_config_init, \

.get_wol = dp83822_get_wol, \

.set_wol = dp83822_set_wol, \

.ack_interrupt = dp83822_ack_interrupt, \

.config_intr = dp83822_config_intr, \

.suspend = dp83822_suspend, \

.resume = dp83822_resume, \

}

static struct phy_driver dp83822_driver[] = {

DP83822_PHY_DRIVER(DP83822_PHY_ID, "TI DP83822"),

DP83822_PHY_DRIVER(DP83825I_PHY_ID, "TI DP83825I"),

};

module_phy_driver(dp83822_driver);

static struct mdio_device_id __maybe_unused dp83822_tbl[] = {

{ DP83822_PHY_ID, 0xfffffff0 },

{ DP83825I_PHY_ID, 0xfffffff0 },

{ },

};

MODULE_DEVICE_TABLE(mdio, dp83822_tbl);

MODULE_DESCRIPTION("Texas Instruments DP83822 PHY driver");

MODULE_AUTHOR("Dan Murphy <dmurphy@ti.com");

MODULE_LICENSE("GPL v2");

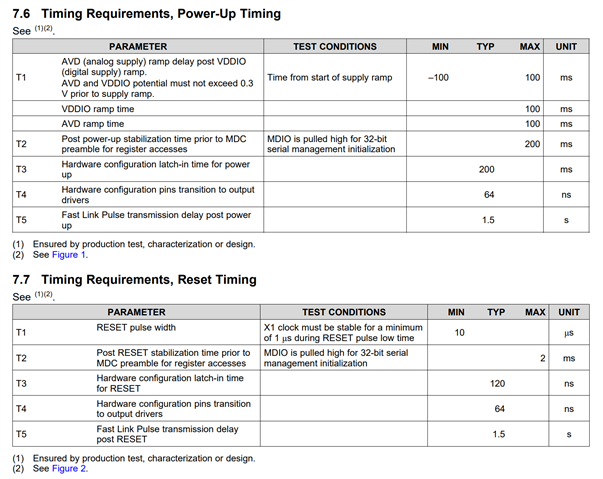

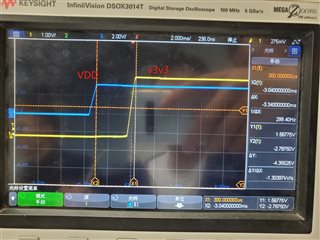

Hello,

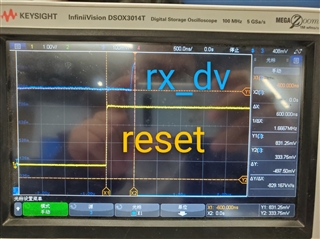

Thank for the file. The scope picture is not clear, is it indicating the pin strap level?

The 0x467 status is 2001 meaning RX_d0 and LED_0 ( reserved) pin strap is configured. Can you please check the same.

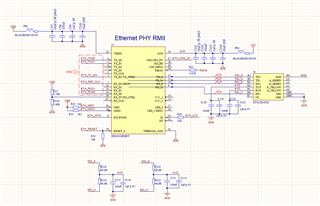

If possible, please share the schematics for review.

Also did you have a chance look into the below that i mentioned in my previous thread

On the hardware, can you please check if any of the other pin straps made and if those works.

Can you please measure the voltage for the pin and the resistors values are as below.

Can you please check the reset timing. If the reset is controlled by a pin, can you please do a hard reset after full boot and follow the recommended timing.

Thanks

Sreenivasa

Hello Sreenivasa :

Good morning, Thank you.

Reset time is 800us. The oscilloscope has been used to confirm it. My dts is follow this picture.

PINS voltage is

Hello bingan zhang

Thank you for the mail and good day to you.

I looked at the schematic and measurements and have some questions

Measurements:

I assume you measured the voltage after the device came out of reset.

The Pin straps are latched during reset. Can you place the device under the reset and measure the voltage.

Schematics

I see that you connected the VDD to pin straps before the caps and connecting to vddio after the caps. I would assume the VDDIO supply ramp up would be delayed due to the caps.

The power supply needs to be table when the device comes out of reset to latch the strap configurations.

You could do this by

1. for testing, can you increase the reset to > 20ms or more and test. Based on the results you could optimize.

Alternatively

2. You can do a hard reset once the host has completed the boot assuming the power supply is stable by that time.

Regards,

Sreenivasa

| PIN | PIN Name | Voltage | PIN | PIN Name | Voltage |

| 1 | RX_D3 | 0 | 17 | LED_0 | 3.2 |

| 2 | TX_CLK | 0 | 18 | RESET_N | 0 |

| 3 | TX_EN/TX_CTRL | 0 | 19 | MDIO | 3.295 |

| 4 | TX_D0 | 0 | 20 | MDC | 0.071 |

| 5 | TX_D1 | 0 | 21 | VDDIO | 3.295 |

| 6 | TX_D2 | 0 | 22 | XO | |

| 7 | TX_D3 | 0 | 23 | XI | |

| 8 | INT/PWDN_N | 3.288 | 24 | LED_1/GPIO1 | 0.004 |

| 9 | RD_M | 3.29 | 25 | RX_CLK | 0 |

| 10 | RD_P | 3.29 | 26 | RX_DV/RX_CTRL | 0.833 |

| 11 | TD_M | 3.29 | 27 | CRS/CRS_DV | 3.226 |

| 12 | TD_P | 3.29 | 28 | RX_ER | 3.225 |

| 13 | NC | 0.063 | 29 | COL/GPIO2 | 3.223 |

| 14 | AVD | 3.278 | 30 | RX_D0 | 0 |

| 15 | NC | 0.692 | 31 | RX_D1 | 0 |

| 16 | RBIAS | 0.000 | 32 | RX_D2 | 0 |

reset time is 130ms, The phenomenon is the same. Tks, Regards

Hello bingan zhang

Thank you for the mail and good day to you.

Thank you for the measurement, the measured voltage across RX_DV seems fine.

Can you please check if your are following the below timing and also toggling the reset as shown below in the reset timing after the power-up timing is complete.

Regards,

Sreenivasa

Hello Sreenivas:

Thank you. I have a questions. I measured the reset time. The MDC time(T2) is 31ms. How to measure Latch-in time(T3). Maybe T3 is just equeal to T2. That's too short a time.

Hello Sreenivasa.

Let me just make sure, Time is too short?

And How to measure Latch-in time(T3).

Thank you.

Hello bingan zhang

This is an internal timing, please ensure T2 timing is followed. please check the same.

Regards,

Sreenivasa

Hello Sreenivasa:

Good day to you.

The specification of 'max 2ms' seems very strange to me. it seems a strange design as puts difficult timing requirements onto a typical linux MAC. Our picture is: Ohh, the "upload" button is not found. I can't upload pictures.

Can you explain to me the time of latch-in? How to control?? Thank you.

[ 3.277060] In stmmac_mdio_reset!!! --------->reset 3.277060

[ 3.363562] libphy: stmmac: probed

[ 3.368963] of_mdiobus_register:230

[ 3.368973] of_mdiobus_register:235 addr=1

[ 3.379409] of_mdiobus_register:244 addr=1 is phy ------>register phy 3.379409

[ 3.382044] of_mdiobus_register:259 rc=0

[ 3.386884] IN stmmac_mdio_register!!!! 368

The time interval is 102ms.

Regards,

BINGAN

Hello bingan zhang

Good day to you.

To start with are you able to read the pin straps now? When are you trying to read the straps, during power up or later.

Regarding the timing

During power up:

Ensure the system is in reset_n till power is stabilized. Time depends on the system.

The hardware latch up time for the straps is 200ms and the MDC stabilization time is 200ms. Please provide a time of > hardware latching time before reading the register.

Reset (after power up)

After power up of the system, linux boot up, power supply stabilization, , you can toggle the reset_n for a time > 10us to do a hard reset.

The hardware latchup time for is 120ns.

The MDC stabilization time is 2ms. Please allow > 2 ms before accessing the register.

Regards,

Sreenivasa

Hello Sreenivasa:

So we start reading this register, read 0x467 is 0x2001. It's error! I can't figure it out.

Does the power up time make sense? The hardware configuration will be latched after reset.

Hello bingan zhang

Thank you for the mail.

Sorry, i could not understand your message fully.

Please see some notes for debug:

What is the initial reset time you have. If the supply ramp is slow, please increase the initial reset time. If the ethernet clock is not available, further increase the reset period.

After performing the reset of the device, are you waiting for > 200ms before reading the register?

Alternatively, After power stabilization

Can you perform a reset toggle > 10us, wait for > 10ms and read the registers. Assumption is ethernet clock is available.

Thanks

Sreenivasa

Hello Sreenivasa:

Yes,reset toggle is 30ms. and wait time is 31ms for control mdio bus. the clock is 25M.

All are normal, that is, 0x467 is abnormal. I was about to cry.

Hello bingan zhang

We will do our bet to resolve the issue.

Are you toggling the reset after ensuring the power is stable.

After how much time is the toggling happening after power up. What is the state of the supply.

Can you remove C97, C99, C101 and C103 and test.

Have you probed the MDIO signals and do they look good.

Regards,

Sreenivaa

Hello Sreenivasa:

Yes.

The time is too long.Because first uboot, then kernel toggling reset gpio.

I removed the Capacitors, the result is the same.

MDIO signal, I can read the phy register. mean it's okay.

Thank you .

Hello Sreenivasa:

Good morining.

Refer to this website: https://e2e.ti.com/support/interface/f/interface-forum/682354/dp83822i-phy-not-stable-random-operation-behavior-latch-in-voltages-do-not-match-register-values-in-0x467-0x468

I use the following sequence

And the result of that reading is 0x0FE3. It's very interesting.

Hello bingan zhang

Good day. Its good Friday here and we have holiday. Thank you for the efforts and appreciate the same.

The register reading seem to match the hardware configuration.

I assume that the hardware working as expected and you are all set now.

Regards,

Sreenivasa

Hello Sreenivasa :

Thank you. Happy holiday!

Read the 0x467 register directly. The value is correct. It's 0xfe3. It is the expected.

Our network card is still not working properly.

Hello bingan zhang

Good day to you and sorry to note that the configuration still does not work.

Have you probed the signals to ensure that the device is in the required configuration.

I would suggest you to start a new thread with the support required.

Good luck.

Regards,

Sreenivasa

Sreenivasa ,thank you!!!

Yup,

I used to use phy_read_mmd to read, It's 0xfe3. I used to use phy_read to read, it's 0x2001.

I'm going to measure the waveform to see if it conforms to the RMII protocol.

Hello Sreenivasa .

Could you please tell me how to do loopback test?

Do I need a board like DP83822 EVM board? Thank you very much

Hello bingan zhang

Greetings to you.

I would assume you want to do loopback test on your board that connects to the link partner.

Please refer to 8.4.8 Loopback Modes to understand the available options.

If you have an EVM, you could use it to do a quick test.

Regards,

Sreenivasa

Thank you! Sreenivasa .

How do I check whether a test succeeds or fails. I'm having trouble reading the documentation.

Hello bingan zhang

Can you please share the loopback setup you have made.

Alternatively, please refer to . 0x0016 BIST Control Register (BISCR).

Regards,

Sreenivasa

Thank you Sreenivasa . I'm working fine under uboot/ Right now I'm looking for kernel-related information. I dont have EVM board, so I shouldnt be able to test loopback.

Hello bingan zhang ,

Thank you for letting me know. A quick summary on the resolution would help.

Regards,

Sreenivasa