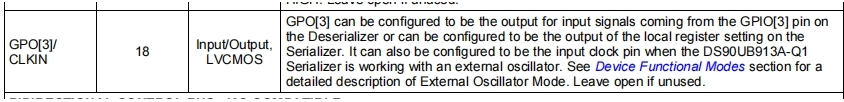

We are using ds90ub913 SerDes to use gpio3 as CLKIN function (external crystal oscillator input, frequency is 37.125mhz). At present, we encounter the following problems, in which we use VDDIO = 2.8V

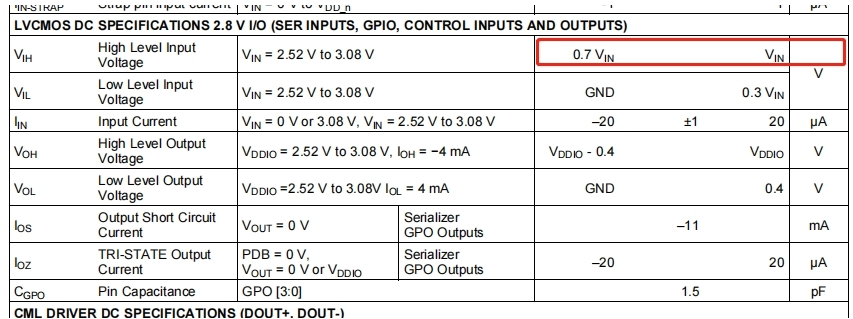

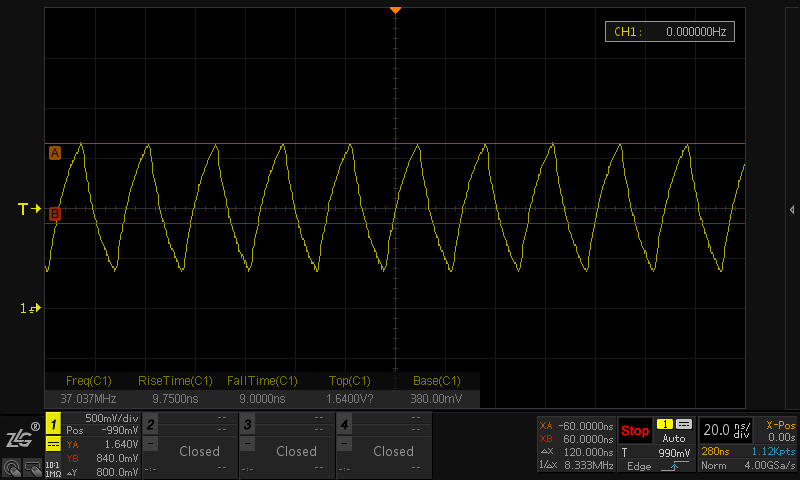

We actually measured the input signal quality of CLKIN, and found that the maximum value of CLK is only about 1.64v (the measured waveform is shown in the attachment). According to lvcmos, the following electrical properties can not reach the minimum value of VIH, but we actually tested some samples, and there is no problem

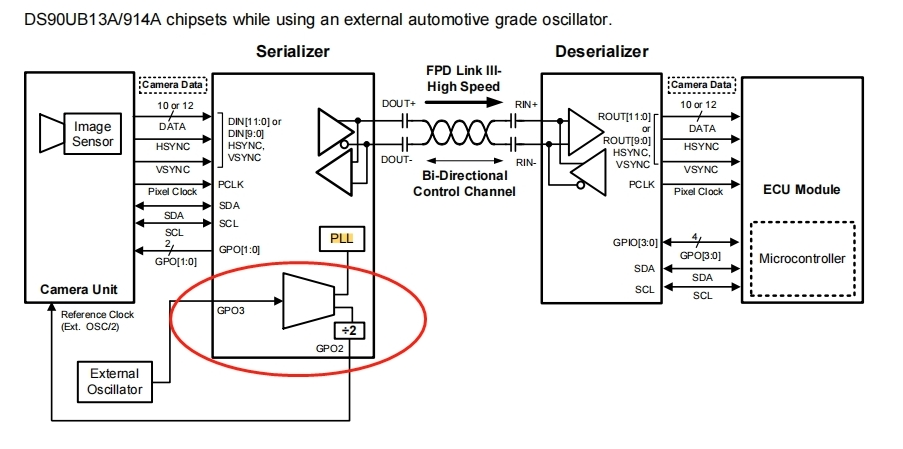

Look at the internal block diagram of the chip. When gpio3 is used as CLKIN, it is mainly used for PLL

Based on the above, I would like to ask: when gpio3 is used as clock input, what are the specific requirements of its electrical parameters? Is lvcmos level required as GPIO? Is it possible to meet the electrical property requirements of vddpll = 1.8V?