Hi Team,

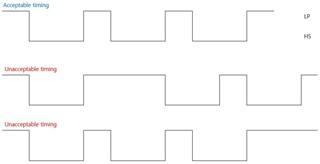

My customer is considering the design for video transmission through SerDes such as FPGA1 -> CSI-2(A) -> 953 -> 954 -> CSI-2(B) -> FPGA2. The CSI-2(A) data from FPGA1 has the fixed line-blanking like a picture below, and also CSI-2(B) data to FPGA2 has the fixed line-blanking which same as CSI-2(A). That is my customer's requirement. Is there any problem on this case? Please let me know it.

Regards,