Part Number: DP83822I

Hello,

I'm working with a board in which your device is driven with a MAC whose GPIO are in weak PU after reset.

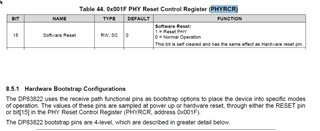

This causes a wrong sampling of RXD0-- RXD3 strap resistors. The device's reset is shared with the MCU, so my only option for a correct sampling of the strap resistors is to

force SW reset by means of PHYCR[15] after having disabled the PU resistors in the MAC's GPIO.

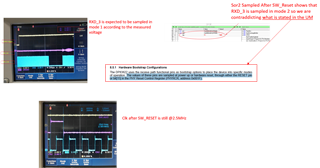

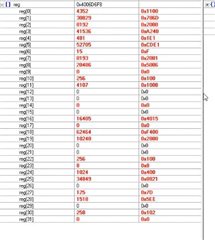

The configuration of Strap Latch-In Registers SOR1 and SOR2 after the physical reset is:

SOR1=0x5FD3;

SOR2=0x5

The PHYCR reset is launched waiting long enough (couple of seconds) after the GPIO configuration in order to let the nodes stabilize to the expected value.

what I see is that after reset is complete nothing changes in the values of SOR1 & SOR2.

Do you have any suggestions?

Another question: if I wanted to counter the weak PU with an additional PD, How far can I go with the value of the external PD in order to avoid stressing the phy's output buffer?

thanks so much for your support

Best Regards,

G