Dear team,

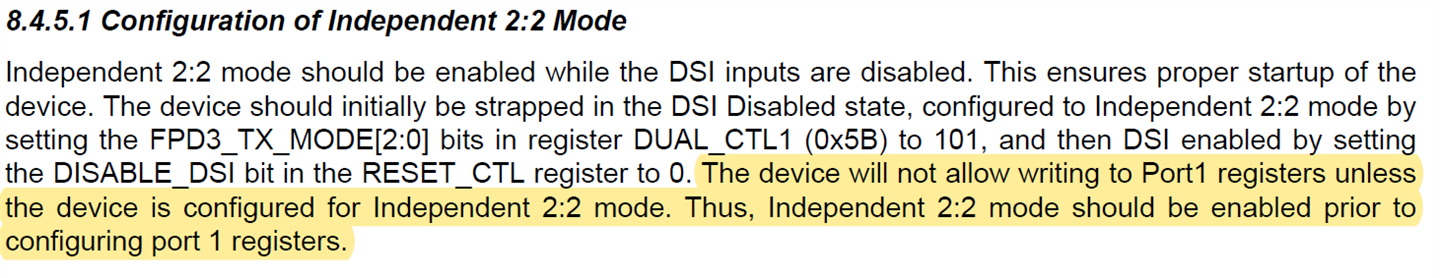

Currently my customer uses 941's independent mode to drive two displays, display 1 is 1920*720(port 0,948) which can display normally. And the display 2 is 800*480(port 1,928) which isn't brought up yet.

Currently my customer uses 941's independent mode to drive two displays, display 1 is 1920*720(port 0,948) which can display normally. And the display 2 is 800*480(port 1,928) which isn't brought up yet.

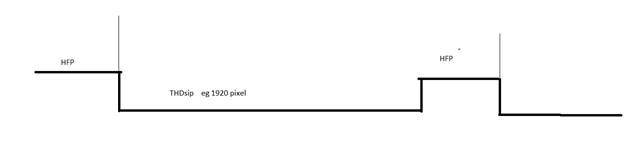

1. We run the pattern(internal timing) on port 1 from 941 side, but display 2 still failed to display. When we connect display 1 to port 1 and run pattern(internal timing) from 941 side, and display 1 works normally. Display 2 is HV mode screen but display 1 is DE mode screen. For these two different modes, is there any different for the pattern code?

1. We run the pattern(internal timing) on port 1 from 941 side, but display 2 still failed to display. When we connect display 1 to port 1 and run pattern(internal timing) from 941 side, and display 1 works normally. Display 2 is HV mode screen but display 1 is DE mode screen. For these two different modes, is there any different for the pattern code?

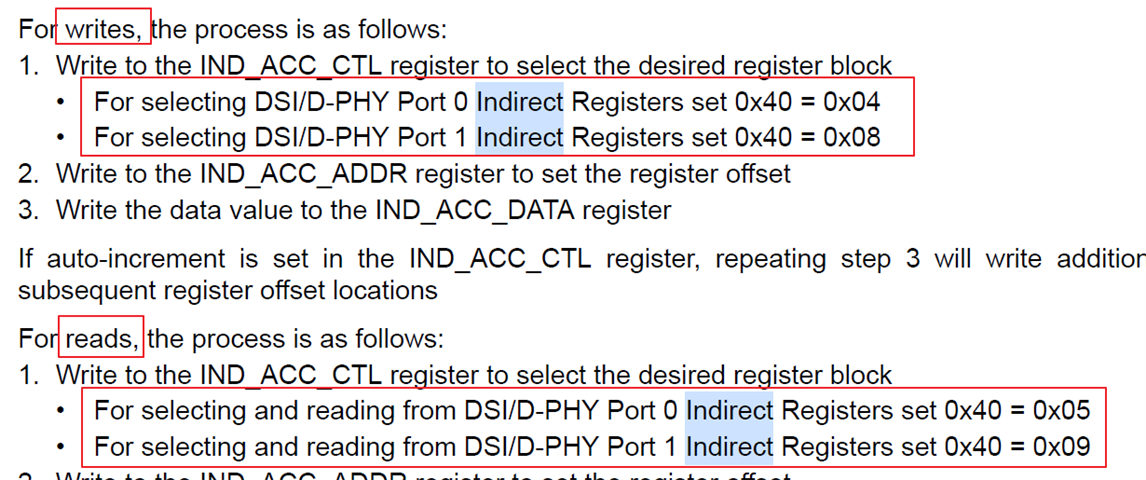

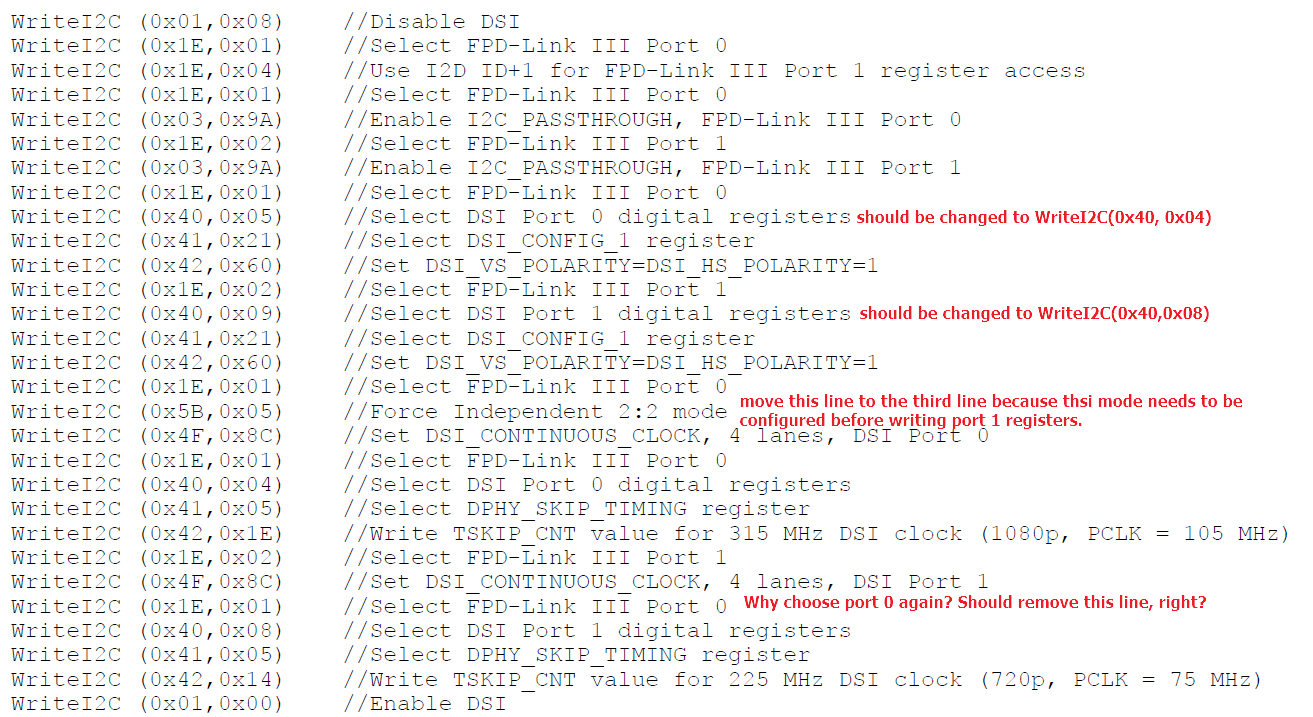

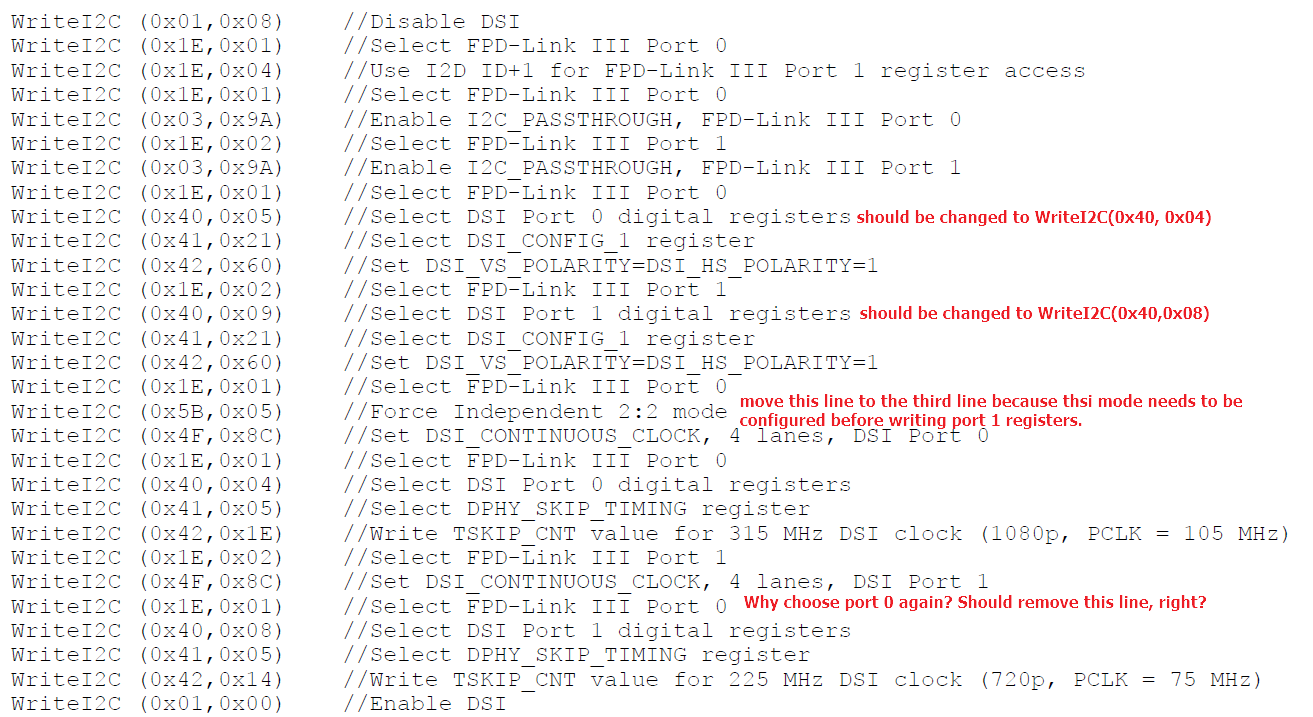

2. There is a example code for independent mode. I see some configuration is strange, could you please help check?

Thanks & Best Regards,

Sherry