Other Parts Discussed in Thread: SN65DSI86

Hi Sir,

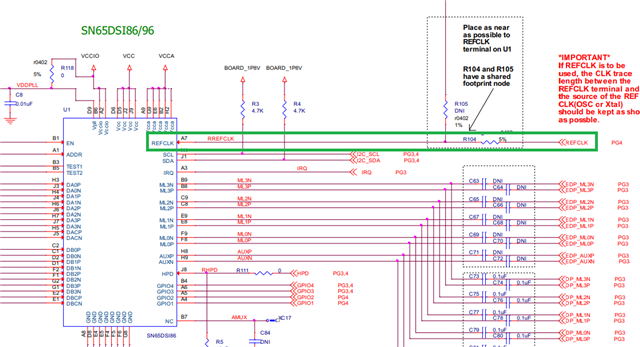

I design SN65DSI86 to do the function of MIPI-DSI to eDP.

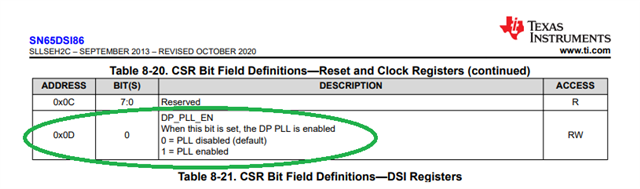

But it occur PLL unlock issue after setting the DP_PLL enable in the register.

It seems like the below issue before.

Could you help me check the issue ?

Thank for your help!

Sincerely,

Shichin