hi TI,

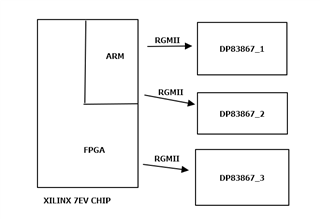

Now,I draw a sch about 7ev(arm+fpga)+3*dp83867.two dp83867 are connected to the ARM side,the other dp83867 is connected to the fpga side.

the three dp83867s can work well at 100Mbps mode,but can't work well at 1000Mbps mode.I did some experiments as follow:

1、our card is connected to the PC,then ping the three eth,it's ok;

2、we use the iperf3 command to test the eth,the rx speed is only 230Mbps.and the tx speed is 170Mbps.

3、the voltage and the 25MHz reference clk are good.

4、the RGMII length is about 3000mil(clk,data).

5、I test the Far-End (Reverse) Loopback,the link partner can generate the original data,and can receive the data without err.

6、release the loopback, then use the iperf3 command to test the eth,the rx speed is about 230Mbps.and the tx speed is about 170Mbps.

check the ifconfig,RX receive errors=overruns+frame.then Modify the MTU and ring buffer,the effect is not good.

Can you give me the idea about debug the dp83867 at 1000M mode?thank you.