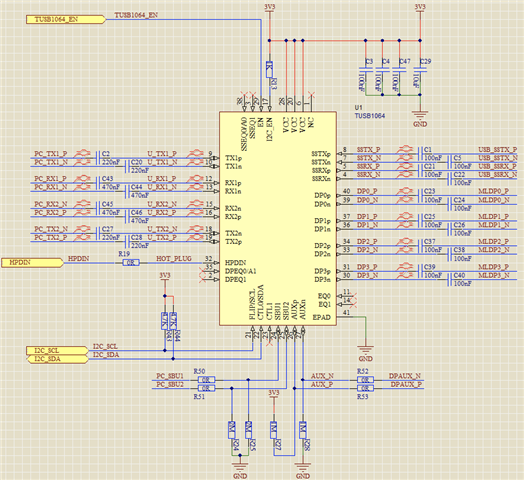

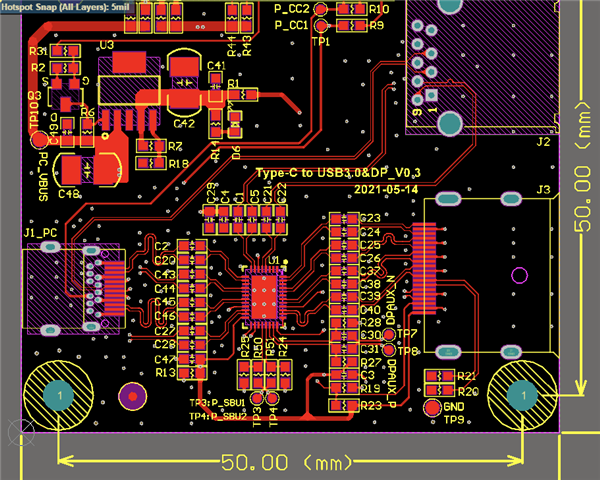

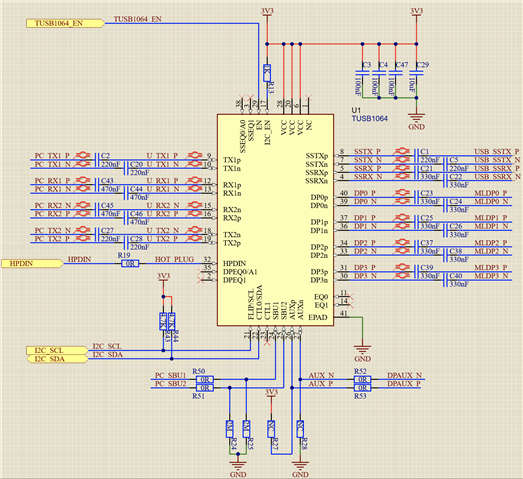

Part Number: TUSB1064RNQEVM

Other Parts Discussed in Thread: TPS65982, TUSB1064

Hi TI expert

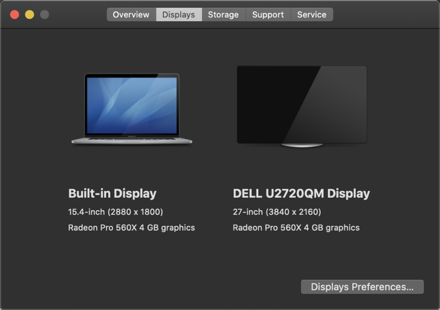

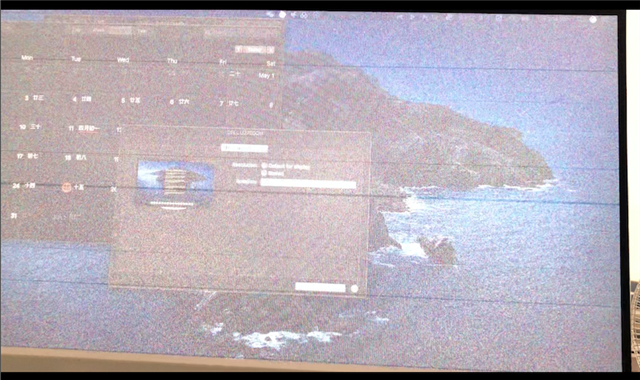

When I use the TUSB1064RNQEVM, the USB 3.0 flash work well, but the DP interface still have some problem.

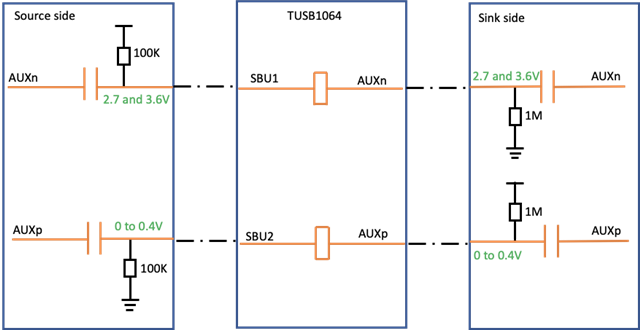

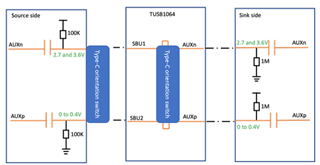

1. The EVM default R12 and R13 resister is't soldering. and can't capture any wave form form AUXn and AUXp.

2. Then soldering the R12 and R13 with 1M resister. there are wave form from AUXp and AUXn, but AUXp wave form is poorly.

3. How can I get the TUSB1064RNQEVM development step?

4. I can't search the TPS65986 data sheet, can I recommend the TPS65982 data sheet?

5. Attachment is the step record that I had do .