Dear Team,

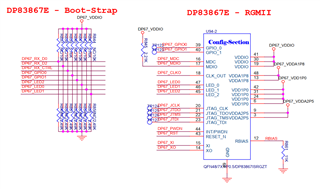

We use the DP83867E as an RGMII PHY, and connect to our MAC Controller, but we observed an anomaly in the RX_CTRL output through the oscilloscope. Detail configuration is as follows:

1. Enable the LOOPBACK Bit of Basic Mode Control Register

2. Config the DUPLEX MODE of Basic Mode Control Register to "Full Duplex operation"

3. Config the TX FIFO Depth and RX FIFO Depth of PHY Control Register

4. Config the RGMII_TX_CLK_DELAY and RGMII_RX_CLK_DELAY of RGMII Control Register to "RGMII transmit/receive clock is shifted relative to transmit/receive data"

5. Config the RGMII_TX_DELAY_CTRL and RGMII_RX_DELAY_CTRL of RGMII Delay Control Register to 4.00 nS

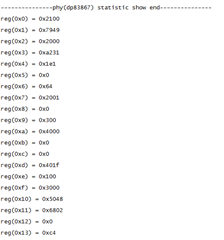

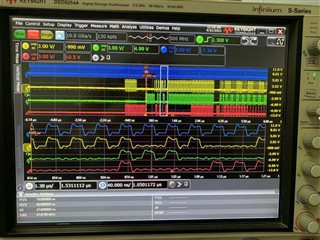

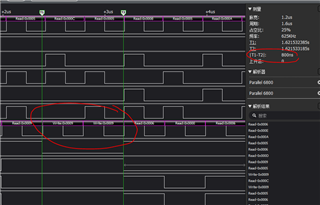

The Figures as follows are captured by the Logic Analysis. As you can see from the Figure_1, the TX_CTRL from MAC Controller is always output High Level, But the RX_CTRL from DP83867E will generate a Low Level pulses periodically. Cycle time is about 321uS and Low Level duration is 80nS. And the Data is 0x9, 0x9. More detail info please see the Figure 2 and 3

The output of RX_CTRL is not what we expected, and it caused the MAC Controller receive the wrong data (or means lost some valid data)

Please explain this phenomenon and provide a solution. Thanks !