Dear team,

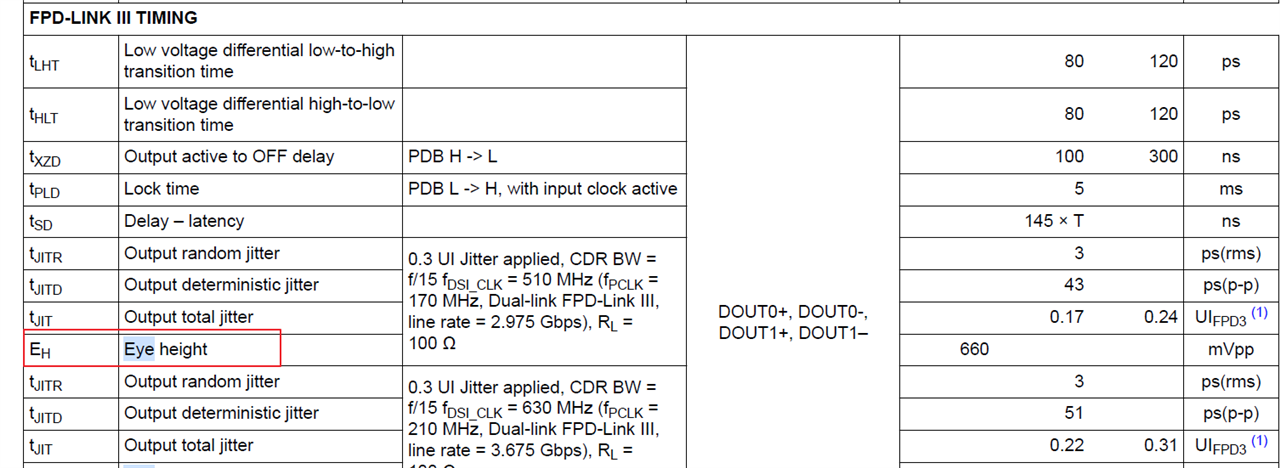

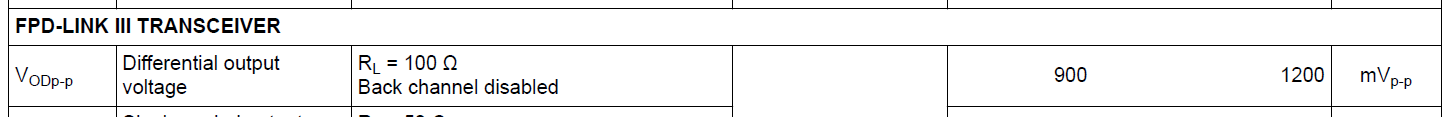

Currently my customer test below parameter, but the test result is only around 650mV which is smaller 900mV. Is there any special requirements for below spec? The BW of the oscilloscope is 13GHz, sample rate is 40GSa/s, and the differential probe is 12GHz. We add the 100ohm, and we still connect to the display when testing. Once disconnect the display, there is no output on DOUT pin.

Thanks & Best Regards,

Sherry