Part Number: TPS65994AD

Hi,

My design is leveraging from Intel TGL DDR4 RVP. i.e. having a TPS65994AD connect to 2 Burnside Bridge.

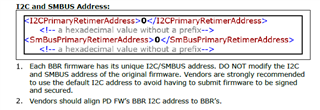

Refer to Intel doc #636184,

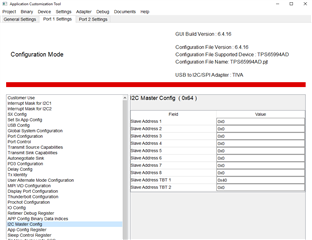

And from TPS6599x Application Customization Tool,

Port 1 I2C slave address for TBT is default 0x40 & Port 2 I2C Slave for TBT is default 0x41.

But BBR NVM state I2C Primary & secondary Retimer Address is default 0. The Intel doc even mentioned "DO NOT modify the I2C Address".

Question:

1. Should the the address in "Slave Address TBT 1" (in TI Application Tool) same as the I2C Retimer Address (in BBR NVM)?

2. if yes, is this means I should set the I2CPrimaryRetimerAddress to be 40 & I2CSecondaryRetimerAddress to be 41? or change the I2C slave address for both port to be 0 in TI Application tool?

Thank you.

Regards,

Alice