Part Number: DP83TG720S-Q1

Hi

I need to test the DP83TG720S-Q1 (SGMII mode) in loopback mode, writing :

reg[0x0000] = 0x4140, loopback is not working.

Do you detail me the procedure to have any (simplest) loopback mode on the PHY.

Regards

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: DP83TG720S-Q1

Hi

I need to test the DP83TG720S-Q1 (SGMII mode) in loopback mode, writing :

reg[0x0000] = 0x4140, loopback is not working.

Do you detail me the procedure to have any (simplest) loopback mode on the PHY.

Regards

Thank you for the query.

Please refer to

7.3.1.3 Built-In Self-Test For Datapath

Can you please share some additional information of the board being used and provide some details on how the tests being performed including what is being tested as pass fail criteria

Regards,

Sreenivasa

Hello Sreenivasa

I am running on a new evaluation board, where this transceiver is wired in SGMII (4-wire) -> RX +- and TX +-

Yes I am point to: 7.3.1.3 Built-In Self-Test For Datapath

In particular, I look at: Table 7-2. Datapath BIST Programming and SGMII loopback.

Via MDIO bus I am able to configure the device and, see dump below:

reg = (

0x4140, -> 1b1 = MII loopback

0x0145, -> link_status = 1 (UP)

0x2000,

0xA284,

0x0,

0x0,

0x0,

0x0,

0x0,

0x0,

0x0,

0x0,

0x0,

0x401F,

0x2024,

0x0,

0x0D, -> mii_loopback, duplex_mode_env, link_status_bit

SGMII loopback via BMCR, is it supposed to work? Which is the SW procedure to have the loopback working?

Or should I implement other loopback mode? My SW has a net stack and able to send and receive frames. So I need a simplest loopback at PHY level.

Regards

peppe

Thank you for the reply.

new evaluation board - did you mean DP83TG720S-Q1 evaluation board?

Do you have a block diagram of the setup you are using to do the loopback tests.

Could you please check if the other loopback modes work.

Can you help me map the register dump above with the address for me to analyze.

Something like this

Register 0000 is: 1140

Register 0001 is: 7949

Register 0002 is: 2000

Register 0003 is: A231

Regards,

Sreenivasa

Hi Sreenivasa

this is aboard where this transceiver is wired in SGMII mode. This is under debugging and I need to understand the exactly procedure to program the loopback modes and the packet gen. I implemented both but for example, I do not know if I need to perform a SW/Hw after the loopback etc.

As example, the cfg_dig_pcs_loopback (bit 7 in the MII_REG_16 Register ) must be programmed?

A simplest internal packet generation can be just done by:

• write : reg[0x0619]=0x1555

• write :reg[0x0624]=0x55BF

I am referring on the following doc:

DP83TG720S-Q1

SNLS604 – SEPTEMBER

Concerning your registers, I am still in loopback mode.

Regards

peppe

Hello Peppe

this is a board where this transceiver is wired in SGMII mode. (I assume you a host)

I do not know if I need to perform a SW/Hw after the loopback etc ( can you please reword the sentence)

Most of the steps are captured in 7.3.1.3.3 Programming Datapath BIST

Also providing a simple block diagram of the setup would help.

Regards,

Sreenivasa

Hello Peppe

One thing i noticed is you are referring to the September datasheet.

Could you please refer to the latest datasheet on TI.com.

Regards,

Sreenivasa

Hi Sreenivasa

thx for your support. Yes I am now using the latest DS.

I noticed that the SGMII is not completing fine the auto-negotiation and the link is down indeed (from SGMII_STATUS Register (Offset = 60Ah)).

I am using 4wiring schema with capacitors of 100ns. Pinstraps look to be ok and also confirmed by 0x45D: MAS/SLV = 1 and MAC_MODE=SGMII.

Do you see anything strange? Welcome advice.

Also from MAC SGMII layer, I see link down and no ane completed.

Best regards

peppe

Hello peppe

Good to know you are using the latest datasheet.

Would it be possible for you to quickly sketch (handmade is fine) the setup that you made to test the loopback.

This would help.

Regards,

Sreenivasa

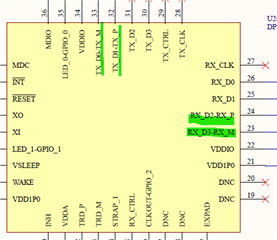

Hi Sreenivasa

sure, let me provide you more details:

|

PIN |

PIN NO. |

Default Value |

Level 2 Mode |

MEANING |

|

RX_D0 |

26 |

OPEN |

1 |

SGMII (4-wire) |

|

RX_D1 |

25 |

OPEN |

1 |

|

|

RX_D2 |

24 |

OPEN |

1 |

|

|

LED_0 |

35 |

2.49KOhm |

2 |

MDI master |

|

LED_1 |

6 |

2.49KOhm |

2 |

Managed Operation |

the PHY driver starts reading the ID registers and these are ok.

Optionally it resets the PHY by using Reg0 or using 0x1F reg.

Then it can set different loopback modes as reported in the section: 7.3.1.3.1 Loopback Modes

optionally the driver can generate the Inbuilt traffic.

The driver also touches the following registers:

Hello Peppe,

Thanks for the inputs.

Let me summarize and ask some questions to constrict the setup

This is a custom built board.

You are looking to use the SGMII interface to the MAC and you have strapped the pins for SGMII. I assume you have take care of the AC coupling requirements.

You are reading the registers through MDIO and MDC.

I also assume you are using the internal packet generator.

Questions

Are you trying to do the loopback from the MAC ? ( figure 7.3 to 7.8 )

Looking forward for you inputs.

Regards,

Sreenivasa

This is a custom built board.

[yes]

You are looking to use the SGMII interface to the MAC and you have strapped the pins for SGMII. I assume you have take care of the AC coupling requirements.

[yes]

You are reading the registers through MDIO and MDC.

[yes]

I also assume you are using the internal packet generator.

[optional]

Questions

Are you trying to do the loopback from the MAC ? ( figure 7.3 to 7.8 )

[yes I tried all them]

Looking forward for you inputs.

many thx. Please consider that the main issue is that the SGMII link is not up.

Is there any programming note you can share me or other things to check if SGMII is ok?

Regards

peppe

Hello Peppe,

Can you please read the below

SGMII_EN bit in SOR_VECTOR_1 Register (Offset = 45Dh) [Reset = 0h]

Also, can you explain more

let me point you that for the SGMII_CTRL_1 Register (Address = 0x608) I read

Hi Sreenivasa.

I solved the issue and now the loopback is working and the SGMII is up. But I have to share the following doubt and please consider it very urgent.

As said in one of my comment above, by strapping pin, the PHY is in configured in managed operation and, as reported in the documentation:

The device (MDI Master mode or MDI Slave mode) automatically enters into standby post power-up and reset so

long that the device is bootstrapped for managed operation.

In fact the LPS_STATUS shows that the PHY is in standby mode.

So setting the bit 0 in the register LPS_CFG3 the PHY goes in normal mode after the power on and my setup is working.

I met the following issue: I changed my strap pin to start in autonomous mode and actually the LPS_STATUS register shows that the PHY is in normal mode but the SGMII doesn't work either loopback. In summary I have to keep the managed mode and then switch in normal mode by SW. Is is expected?

Can you provide me more details about managed and autonomous and the related programming?

Best Regards

peppe

Hello Peppe

Thanks for letting me know on the settings and your efforts to make the SGMII interface work.

The managed mode to normal mode configuration matches the datasheet.

The datasheet provides explanation on managed and autonomous mode and i do not have more detail for now to share.

Regarding the strap being configured to autonomous mode and SGMII not working, let me check if similar behavior has been observed internally.

Regards,

Sreenivasa

Hello Peppe,

For my understanding, are you using the host to do the loopback and verify?

Can you please summarize the method you are following.

Hi Sreenivasa

the method is very simple, the MAC host sends the frames and I get the loopback on PHY. Actually I am using analog loopback.

> The datasheet provides explanation on managed and autonomous mode and i do not have more detail for now to share.

can you point me on those? As said, the autonomous is not working.

But managed is ok after programming the registers.

Regards

peppe

Hello Peppe,

Thank you for the inputs on self test and appreciate the same.

Regarding the autonomous mode , please refer to 7.4 Device Functional Modes.

regards,

Sreenivasa