Part Number: DS90UB928Q-Q1

Other Parts Discussed in Thread: ALP

Hi team,

met an issue on evluation DS90UB928:

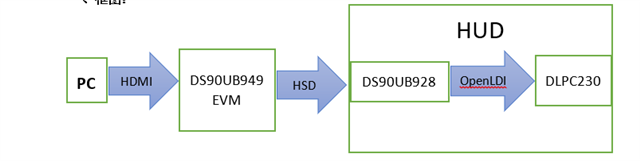

system block below:

The problem now faced:

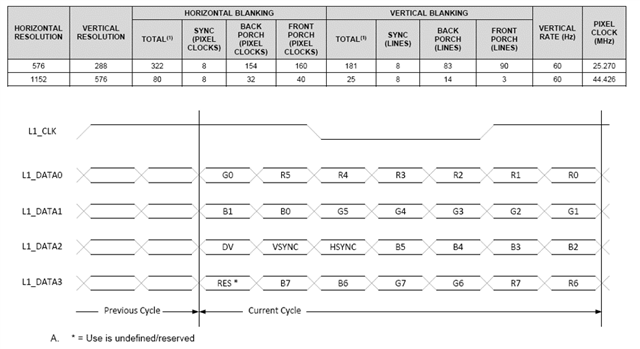

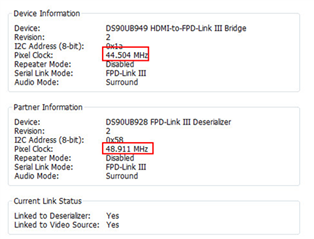

difference ALP data read on PCLK between 928 and 949:

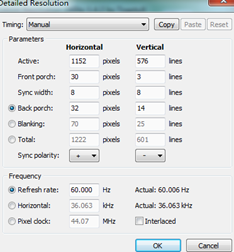

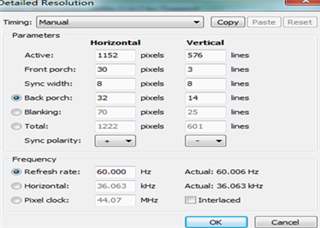

The output setting on PC Side:

Support need:

could you help give some advice to adjust the PCLK on 928 to PC side output setting

BR

Brandon