Part Number: PCA9306

Hi Team,

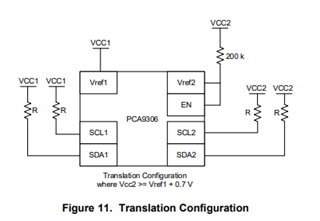

Need your expertise on this. Our customer is currently using the PCA9306 as a level shifter configured in switch configuration (Figure 10 of datasheet).

Operating conditions are as follows:

VREF1 = 1.8V

VREF2 = 3.3V

EN pin is tied to MCU which has a high logic level of 3.3V

Should they be using the translation configuration instead, or can this configuration still work?

Are there any potential risks? Asking for your help as they've already made a significant number of PCBs using this configuration.

Kind Regards,

Jejomar