Part Number: DP83TD510E

Hello,

I am having issues getting a proper link over Single Pair Ethernet with the Ti EVM-Board and our own design.

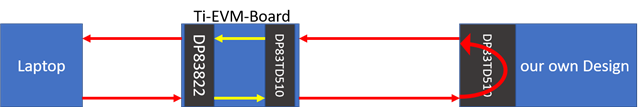

The current setup is:

- Laptop connected over LAN-Cable to the DP83TD510E-EVM Board

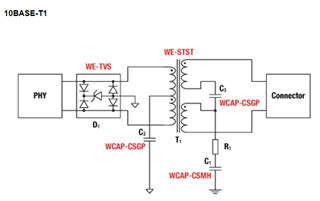

- Twisted pair of copper (~10cm) connected to the EVM-Board and our own Board. Our own Board features also a DP83TD510E, with a 50Mhz oszillator.

- The DP83TD510E on our Board is then set to "Reverse Loopback" (Register 0016 set to 0110) to send the received data back over SPE to the EVM-Board.

- With a packet generator on the laptop we send dummy UDP packets with a frequency of 32Hz to the EVM-Board.

- On the same Laptop a packet sniffer is recording all in- and outgoing packets.

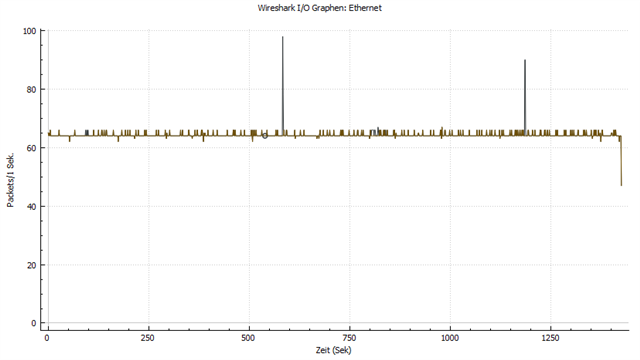

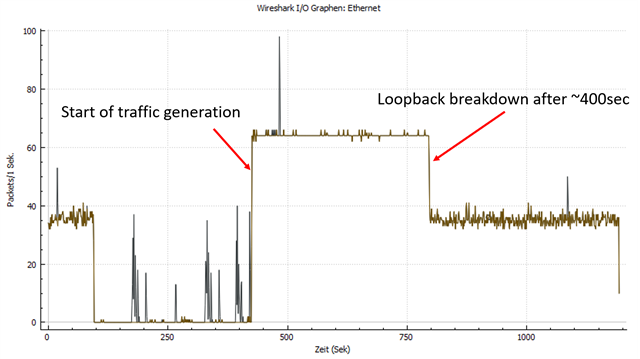

In the first ~400-500 seconds the loopback works flawlessly. But for no reason, after a sertain time no more incoming packets are recorded. The duration of the loopback working is approx. always the same. In the picture below you can see ~64Hz in- & outgoing packet rate, and after the breakdown it drops to 32Hz, which means no more packets are received.

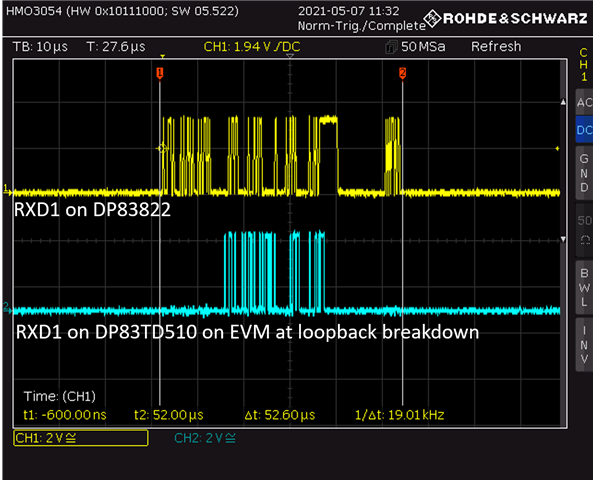

When the loopback is working properly, the RXD0 and RXD1 signals on the EVM-Board of the DP83TD510E look very consistent. When the loopback breaksdown the RXD0 and RXD1 signals tend to be not consistent at all. In the picture below is a example of the signal after loopback breakdown, looks like a part of the packet is missing.

When the loopback stopped working following registers in the DP83TD510E on our own Board are changing:

- 0x15 (RX error count) increases

- 0x17 [2] RMII fifo underflow flag changes to 1

- 0x12D Tx packet error increases

- 0x130 Rx packet error increases

Does anyone have an idea what could be the problem with this setup? Are we missing something?

If any informations are missing, let me know.

Thank you very much!

Kind regards,

Moritz