Support Path: /Product/Development and troubleshooting/

Hi TI Support Team,

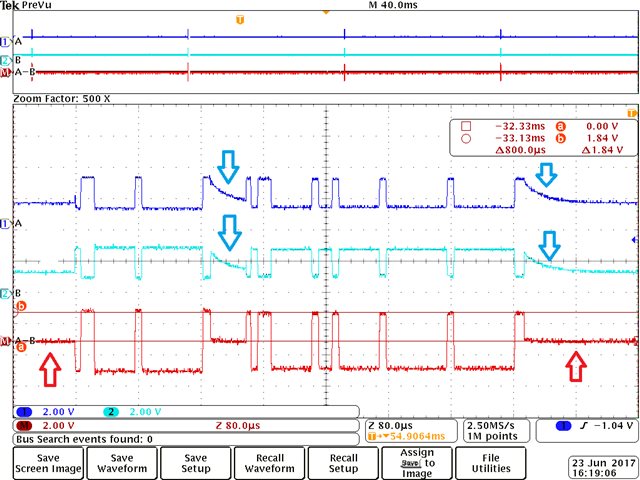

I'm currently testing on the RS-485 differential signal and observe the behaviors as shown in attached scope plot...

I was hoping to have the following demystified:

1. [Highlighted with Red Arrows] One scenario shows that the A-B signal is held HIGH when bus is inactive.

The other scenario shows that the A-B signal is held right in the middle when bus is inactive.

Can anyone please advise which scenario is correct here, according to RS-485 protocol standards?

2. [Highlighted with Blue Arrows] A ramp is separately seen on A or B signal (at the same time point) in between transmissions on the bus. The A-B signal actually cancels that ramp out. Is this typical and acceptable on RS-485 protocol?

Thank you very much in advance for any input!

Sincerely,

Ken