Part Number: tps65986

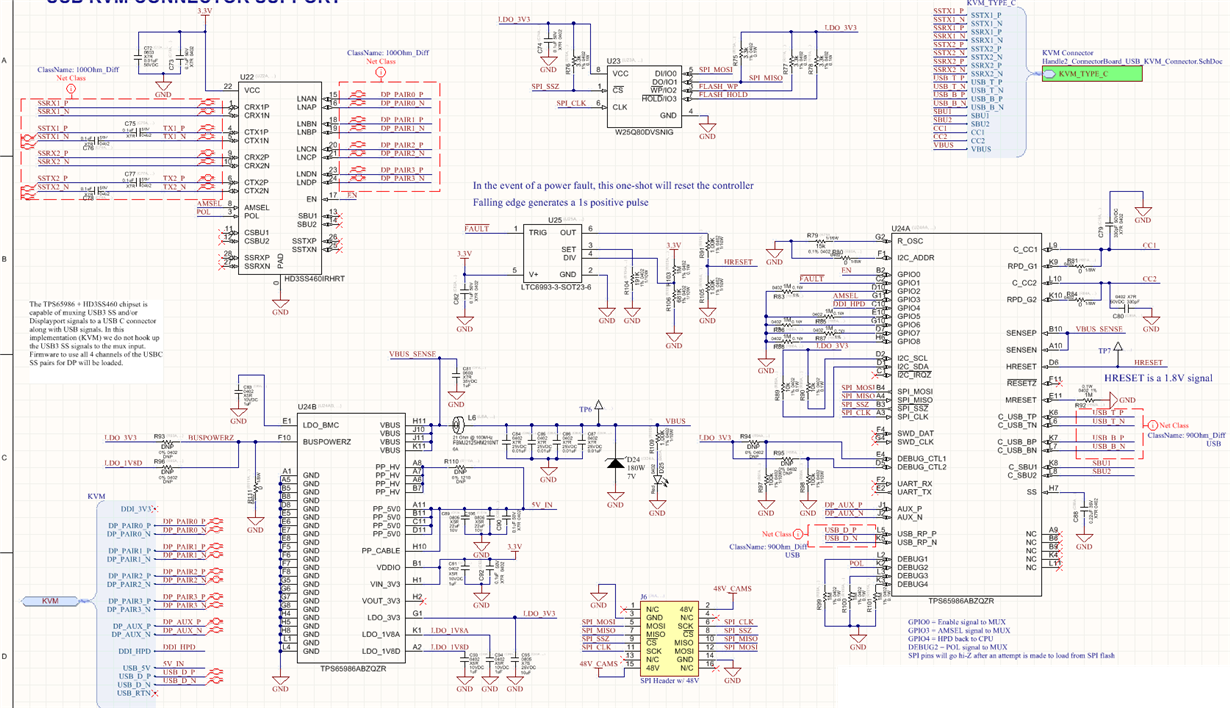

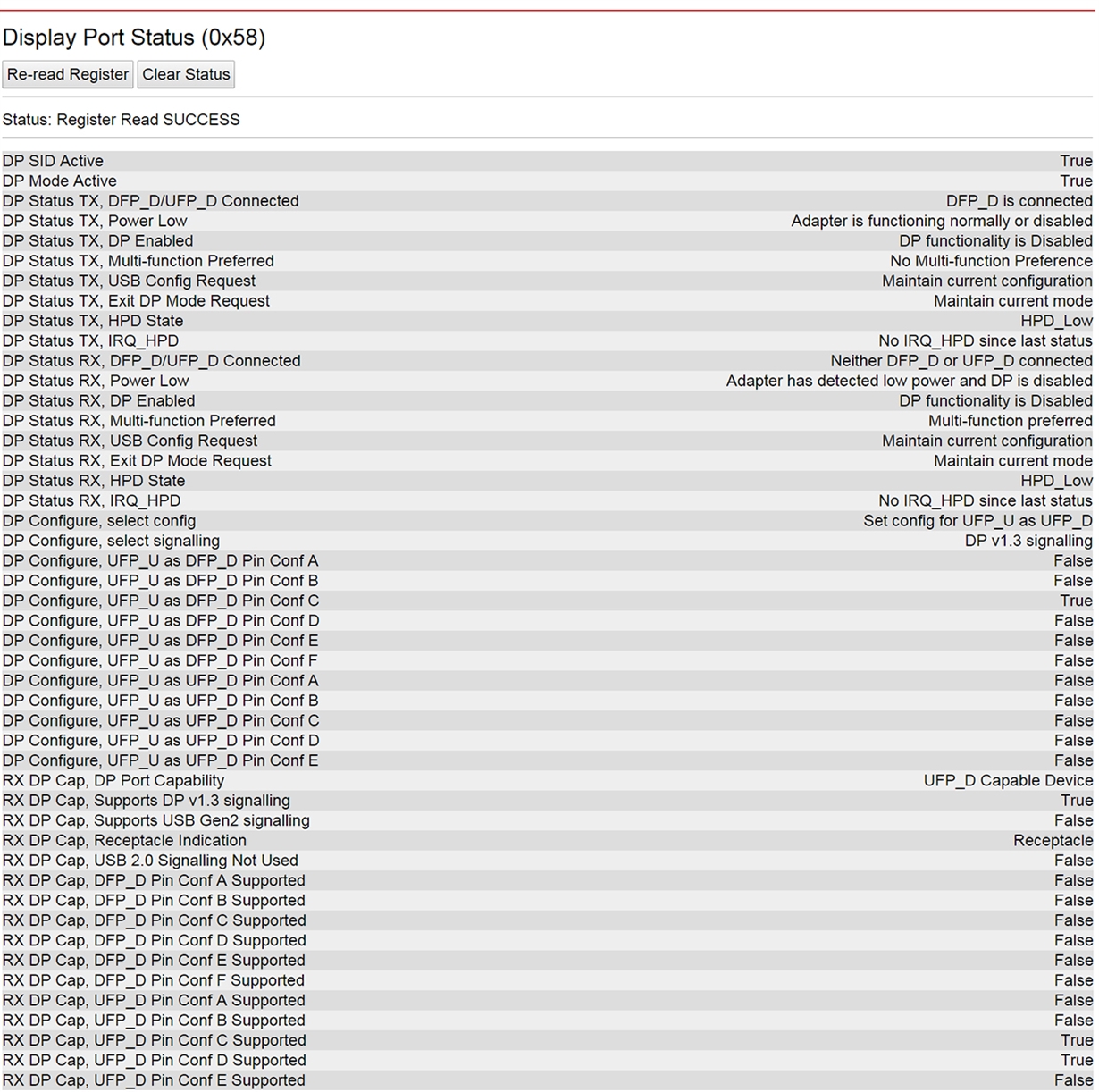

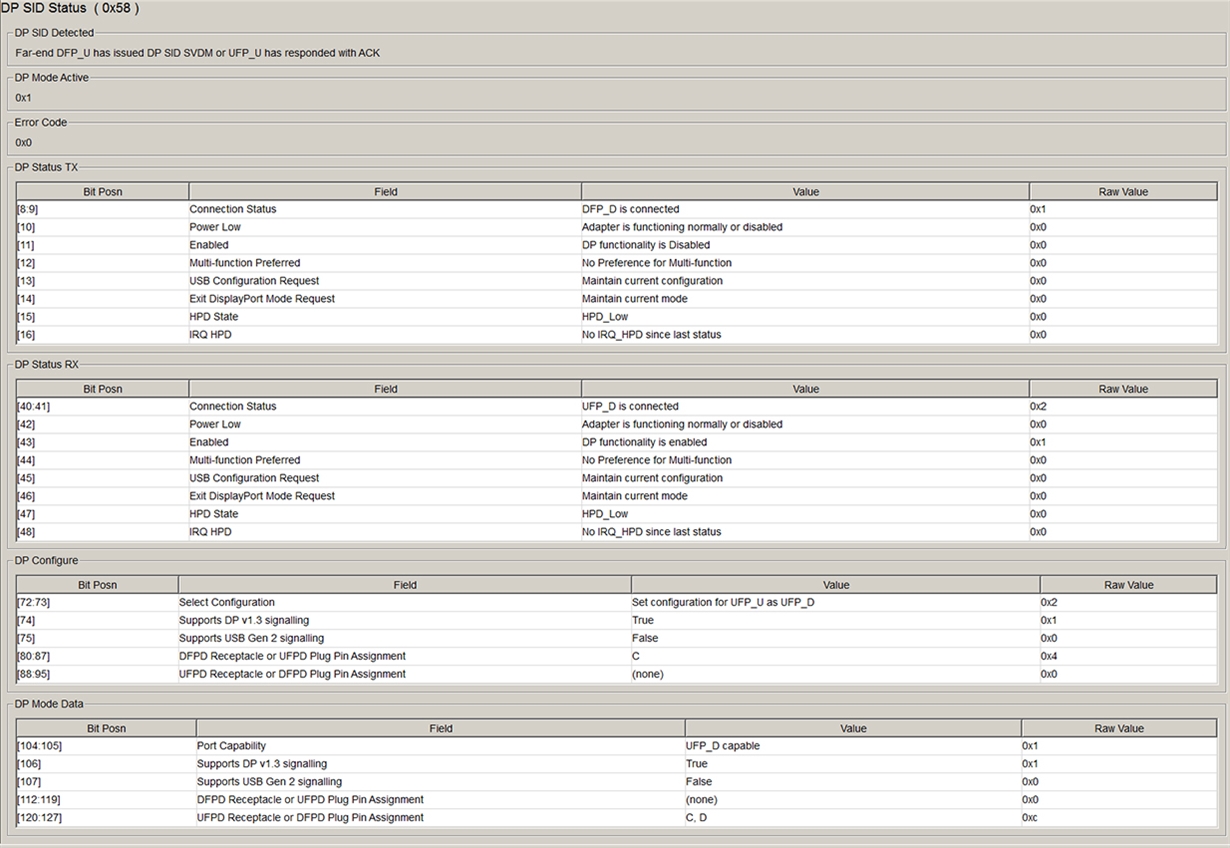

I have my own TPS65986 + HD3SS460 mux DFP implementation that I am trying to get working. I am trying to get a 4 lane DisplayPort + USB2 link working. I am using a TPS65986EVM module with sync board as the UFP and this is connected to a monitor over a DisplayPort cable. So far I cannot get video working. I am able to use a TPS65986EVM module with a source board to connect to the TPS65986EVM+sync board and that seems to work just time.

On my implementation, from what I am able to scope, the mux's Enable pin goes high when the UFP is connected. The AMSEL pin also goes high and the POL pin changes based on the polarity of the USB C cable plugged in. I can scope DP Aux data entering the TPS65986 and leaving on the SBU1/SBU2 pins. However I don't scope any data on the main displayport lanes. The chipset is correctly supplying power to the UFP when it is plugged in.

I am building my application on top of the TPS65986_HD3SS460_DFP_Advanced_v3_10.tpl project. When I apply this same firmware to the TPS65986EVM +source board instead of my implementation, the system works.

I'm pasting my schematic here to have a look at. I drew it based off of the schematic in the EVM user guide and the mux source/sync EVM user guide: http://www.ti.com/lit/pdf/slvuan9

One thing that I notice different about my implementation and the DP-EXPANSION-EVM is the ordering of the 4 DP lanes into the mux. On page 14 the schematic shows the following connections between the DP connector and the mux:

LNA <--> ML1

LNB <--> ML0

LNC <--> ML3

LND <-->ML2

I have my channels hooked up as

LNA <-->ML0

LNB <-->ML1

LNC <-->ML2

LND <-->ML3

Could you comment on why they are wired up this way in the EVM?

Thanks,