Hi Support,

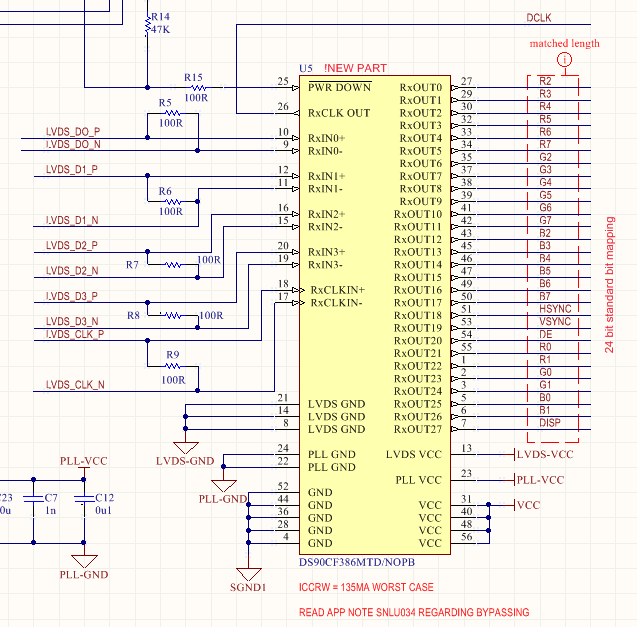

Going to use the DS90CF386 to convert LVDS signal from Freescale iMX6 dual light to RGB display.

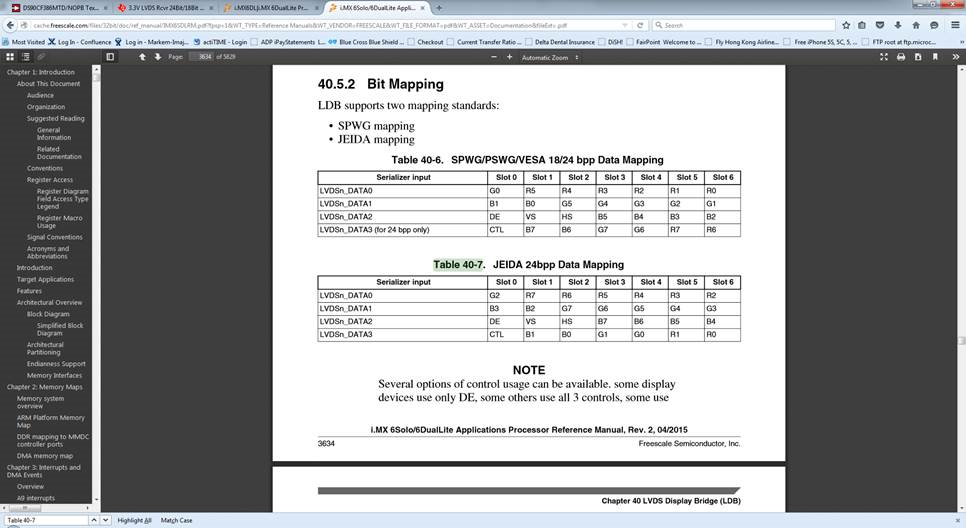

Currently I have a question about the RGB signal mapping from the TI part to the display connectors (using JEIDA mapping).

Please help to check the signal if we have done correctly.

Attached the schematic for the TI de-serializer and the bit mapping of the LVDS signals from imx6 dual light.

Thanks.