Other Parts Discussed in Thread: , ISO1432, ISO1412DWEVM, ISO1452, ISO1412

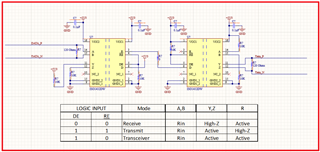

We’re looking to implement a design for a full-duplex asynchronous communication using the ISOW1432.

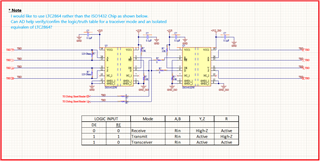

From the ISOW1432 datasheet, Table 2 and Table 3, I'm able to put together a Truth Table and a Schematic that captures the configuration the two modes (Receive and Transmit) modes of operation.

In summary, when the driver enable pin, DE, is logic high, the differential outputs, Y and Z, follow the logic states at data input, D and the receiver is enabled when the receiver enable pin, RE, is logic low.

In addition to the above mentioned modes, I can’t seem to find any reference for the “Transceiver” mode of operation. i.e. the logic combinations for DE and RE_ pins.

From a previous design experience, I’ve used the LTC2864 chip that configuring these pins allowed for the transceiver operation without software intervention and  I was wondering if the ISOW1432 will operate just as the LTC2864 with the truth table shown in the attached image?

I was wondering if the ISOW1432 will operate just as the LTC2864 with the truth table shown in the attached image?