Hello team,

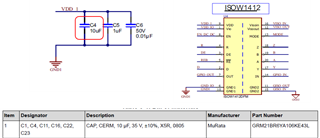

1. Capacitor value

On EVM, a Murata cap is applied as C4. Do we have some recommendation on DC bias and initial tolerances? Also is there a lower limit?

*C4: GRM21BR6YA106KE43L (+/-10% Initial Tolerance, -37.3% DC Bias (@5V))

10uF x (-10%) x (-37.3%) = 5.6uF

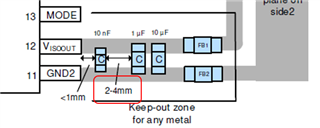

2. 13.1 Layout Guidelines

It says no traces or grounding within 4 mm, is this origin recognized from copper to 11pin, 12pin?

If a 4 mm circle is added to the EVM layout, why would there be a pattern inside the circle around L5?

3. 13.2 Layout Example

What is the reason for the 2-4mm limitation between capacitors?

If the passcon is moved away from the power supply pin, it may affect the stability of the power supply. What happens if the passcon is moved closer to the power supply pin?

Best regards,

Shotaro