Tool/software:

Dear TI Support,

I’m currently working with the ISO1228 device to interface field digital inputs (typically 24–28 VDC) to a microcontroller with isolation.

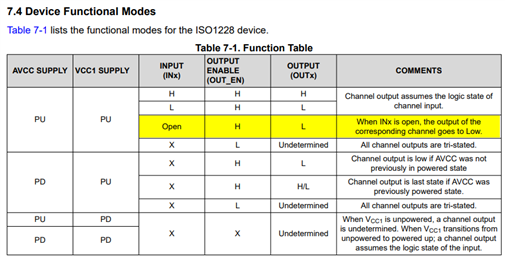

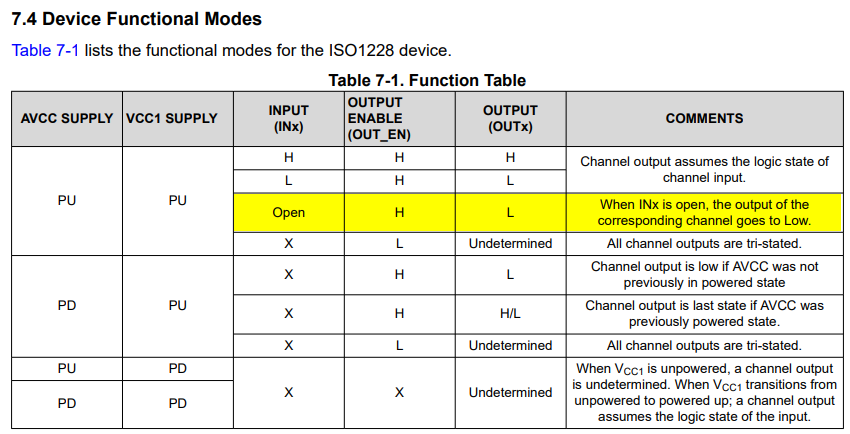

According to the functional table in Section 7.4 of the ISO1228 datasheet, when an input pin (INx) is in an open state, the output (OUTx) goes Low, as described:

“When INx is open, the output of the corresponding channel goes to Low.”

This behavior aligns well with our application. Specifically, we are using ISO1228 to detect discrete input signals in two configurations:

-

Open/GND: where GND = logic LOW, and open = logic HIGH

-

Open/28V: where 28 V = logic HIGH, and open = logic LOW

In both cases, open is treated as a valid logic state, not a fault condition. This is intentional and required behavior in our design.

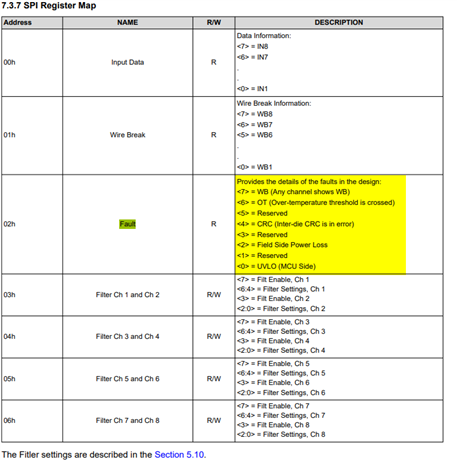

However, I’ve seen some documentation or comments that suggest ISO1228 treats open inputs as undetermined or as a wire-break fault. To avoid any misunderstanding, could you please confirm the following:

-

Is an open INx input consistently interpreted as logic LOW, per Table 7-1?

-

Is this behavior safe and deterministic for production applications?

-

Is there any internal timeout or protection logic that could interfere with intentionally floating inputs in open/GND or open/28V configurations?

We want to ensure ISO1228 behaves predictably when inputs are intentionally left open in these discrete signaling schemes.

I appreciate your support and clarification on this matter.

Best regards,